# 2008

**UMH**

Xavier Dubuc

Voici un résumé de toute la matière à étudier pour l'examen de janvier 2008 du cours de Fonctionnement des Ordinateur donné par Monsieur Luc Onana Alima.

## [FONCTIONNEMENT DES ORDINATEURS : EXAMEN 08]

## Sommaire

|           |                                                    |           |

|-----------|----------------------------------------------------|-----------|

| <b>1.</b> | <b>Introduction aux ordinateurs.....</b>           | <b>7</b>  |

|           | Définition : Architecture des ordinateurs.....     | 7         |

|           | Définition : Organisation des ordinateurs. ....    | 7         |

|           | Fonctions de base d'un ordinateur.....             | 7         |

|           | Structure interne d'un ordinateur. ....            | 7         |

|           | Evolution et performances des ordinateurs. ....    | 8         |

| <b>2.</b> | <b>Première génération d'ordinateurs. ....</b>     | <b>8</b>  |

|           | 1.ENIAC .....                                      | 8         |

|           | 2.IAS (Machine de Von Neumann) .....               | 9         |

|           | Fonctionnement de l'IAS. ....                      | 9         |

| <b>3.</b> | <b>Deuxième génération d'ordinateurs.....</b>      | <b>12</b> |

| <b>4.</b> | <b>Troisième génération d'ordinateurs. ....</b>    | <b>12</b> |

|           | Conception pour la performance.....                | 13        |

|           | Vitesse des microprocesseurs. ....                 | 13        |

|           | Les circuits combinatoires. ....                   | 14        |

|           | Définition.....                                    | 14        |

|           | Multiplexeurs. ....                                | 14        |

|           | Décodeurs.....                                     | 15        |

|           | Tableaux logiques programmables. ....              | 15        |

| <b>5.</b> | <b>Conversion binaire-décimal-hexadécimal.....</b> | <b>15</b> |

|           | •Binaire → Décimal. ....                           | 15        |

|           | •Décimal → Binaire. ....                           | 15        |

|           | •Hexadécimal → Décimal. ....                       | 16        |

|           | •Binaire → Hexadécimal.....                        | 16        |

| <b>6.</b> | <b>La mémoire à lecture seulement. ....</b>        | <b>16</b> |

|           | Définition .....                                   | 16        |

|           | Le problème des additionneurs. ....                | 17        |

| <b>7.</b> | <b>Circuits séquentiels.....</b>                   | <b>17</b> |

|           | •Définition.....                                   | 17        |

|           | •Les bascules.....                                 | 17        |

|           | o    La bascule R-S .....                          | 18        |

|           | o    La bascule R-S avec horloge .....             | 18        |

|                                                                              |           |

|------------------------------------------------------------------------------|-----------|

| ○ La bascule D .....                                                         | 19        |

| ○ La bascule J-K.....                                                        | 19        |

| <b>•Les registres.....</b>                                                   | <b>19</b> |

| <b>•Les compteurs .....</b>                                                  | <b>20</b> |

| <b>8.      Programmation matérielle et programmation logicielle.....</b>     | <b>20</b> |

| <b>•Programmation matérielle .....</b>                                       | <b>20</b> |

| <b>•Programmation logicielle .....</b>                                       | <b>20</b> |

| Comment fournir ces signaux à ce dispositif matériel à usage général ? ..... | 20        |

| <b>9.      Structures d'interconnexion. ....</b>                             | <b>21</b> |

| <b>•Le module mémoire.....</b>                                               | <b>21</b> |

| <b>•Le module d'I/O.....</b>                                                 | <b>21</b> |

| <b>•Le processeur.....</b>                                                   | <b>22</b> |

| <b>Les types de transferts supportés.....</b>                                | <b>22</b> |

| <b>•Interconnexion par bus.....</b>                                          | <b>22</b> |

| ✓ Les bus de données .....                                                   | 23        |

| ✓ Le bus d'adresses.....                                                     | 23        |

| ✓ Utilisation typique du bus d'adresse.....                                  | 23        |

| ✓ Le bus de contrôle .....                                                   | 24        |

| ✓ Quelques commandes typiques des bus de contrôle : .....                    | 24        |

| <b>•Fonctionnement du bus.....</b>                                           | <b>24</b> |

| ♠ Envoi des données.....                                                     | 24        |

| ♠ Demande des données.....                                                   | 25        |

| <b>•Réalisation physique typique d'une interconnexion par bus.....</b>       | <b>25</b> |

| Le bus local .....                                                           | 25        |

| Le bus à haute vitesse.....                                                  | 26        |

| <b>•Les éléments importants dans la conception de bus : .....</b>            | <b>26</b> |

| ○ Le type de bus.....                                                        | 26        |

| ○ La méthode d'arbitrage .....                                               | 26        |

| ○ Le timing .....                                                            | 26        |

| ○ La largeur du bus .....                                                    | 27        |

| ○ Les types de transferts de données.....                                    | 27        |

| <b>•Le PCI .....</b>                                                         | <b>28</b> |

|                                                                                     |           |

|-------------------------------------------------------------------------------------|-----------|

| <b>10. Les mémoires.....</b>                                                        | <b>28</b> |

| ●Caractéristiques des mémoires.....                                                 | 28        |

| ♠ Emplacement.....                                                                  | 29        |

| ♠ Capacité .....                                                                    | 29        |

| ♠ Unité de transfert.....                                                           | 29        |

| ♠ Méthode d'accès .....                                                             | 30        |

| ♠ Performance .....                                                                 | 31        |

| ♠ Le type physique.....                                                             | 31        |

| ♠ Volatile – Non-Volatile .....                                                     | 31        |

| ♠ Organisation .....                                                                | 32        |

| ●Hiérarchie des mémoires.....                                                       | 32        |

| <i>Une hiérarchie typique :</i> .....                                               | 32        |

| Impact : .....                                                                      | 32        |

| Illustration : .....                                                                | 33        |

| Localité des références : .....                                                     | 33        |

| ●La mémoire cache.....                                                              | 33        |

| <i>Une organisation typique de la mémoire cache :</i> .....                         | 35        |

| <b>11. Les mémoires internes.....</b>                                               | <b>35</b> |

| ●Mémoires principales à semi-conducteurs. ....                                      | 35        |

| ●Propriété des cellules mémoires :.....                                             | 36        |

| ●Types de mémoire à semi-conducteurs. (toutes des mémoires à accès aléatoire) ..... | 36        |

| ●La RAM .....                                                                       | 36        |

| ○ Caractéristiques principales : .....                                              | 36        |

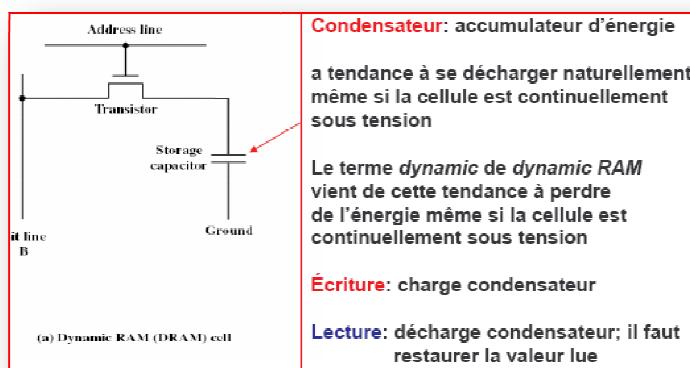

| ○ Structure typique d'une cellule <b>DRAM</b> : .....                               | 37        |

| ○ Caractéristiques : .....                                                          | 37        |

| ●Comparaison entre la DRAM et la SRAM.....                                          | 38        |

| ●Les types de ROM .....                                                             | 38        |

| ○ La ROM .....                                                                      | 38        |

| ○ La PROM .....                                                                     | 38        |

| ○ La mémoire à lecture majoritaire.....                                             | 38        |

| ●Détection et correction d'erreurs. ....                                            | 39        |

| ○ Erreurs permanentes.....                                                          | 39        |

| ○ Erreurs intermittentes.....                                                       | 39        |

|                                                                  |           |

|------------------------------------------------------------------|-----------|

| ○ La logique illustrée .....                                     | 40        |

| ○ Le code de Hamming .....                                       | 40        |

| <b>12. Les mémoires externes.....</b>                            | <b>44</b> |

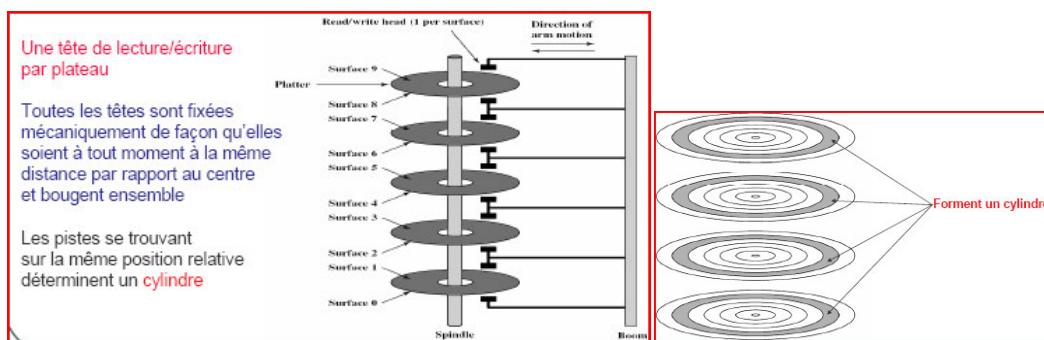

| ● <b>Les disques magnétiques.....</b>                            | <b>44</b> |

| ○ Qu'est-ce que c'est ? .....                                    | 44        |

| ○ Lecture et écriture.....                                       | 44        |

| ○ Organisation .....                                             | 44        |

| ○ Caractéristiques physiques.....                                | 45        |

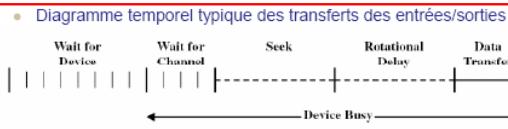

| ○ Paramètres de performance.....                                 | 46        |

| ● <b>RAID .....</b>                                              | <b>46</b> |

| ○ Qu'est-ce que c'est ? .....                                    | 46        |

| ○ Objectifs.....                                                 | 46        |

| ● <b>Bandes Magnétiques .....</b>                                | <b>46</b> |

| <b>13. Les modules d'entrées/sorties.....</b>                    | <b>47</b> |

| ● <b>Interface entre l'ordinateur et le monde extérieur.....</b> | <b>47</b> |

| ● <b>Modèle générique de module d'I/O .....</b>                  | <b>47</b> |

| ● <b>Nécessité .....</b>                                         | <b>47</b> |

| ● <b>Fonctions .....</b>                                         | <b>48</b> |

| ● <b>Unités Périphériques .....</b>                              | <b>48</b> |

| ○ Qu'est-ce que c'est ? .....                                    | 48        |

| ○ Classification.....                                            | 48        |

| ○ Remarque .....                                                 | 48        |

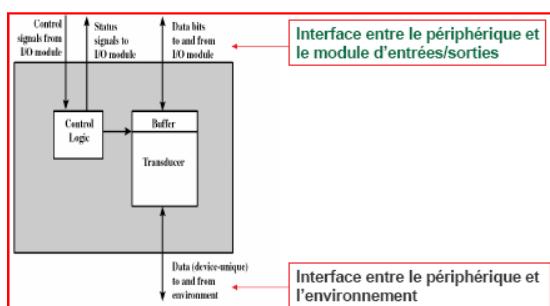

| ○ Schéma général .....                                           | 48        |

| ○ Caractéristiques fondamentales .....                           | 49        |

| ○ Clavier/Ecran .....                                            | 49        |

| ● <b>Retour aux fonctions des modules d'I/O .....</b>            | <b>50</b> |

| ○ Contrôle et timing .....                                       | 50        |

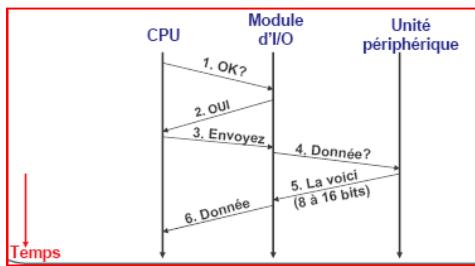

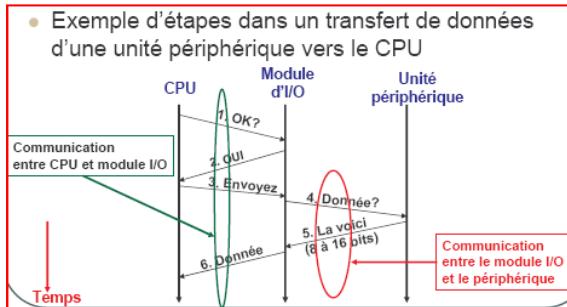

| ○ Communication avec le processeur et l'unité périphérique ..... | 50        |

| ○ Mémorisation temporaire des données .....                      | 50        |

| ○ Détection d'erreurs .....                                      | 51        |

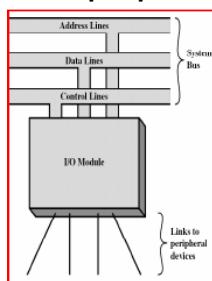

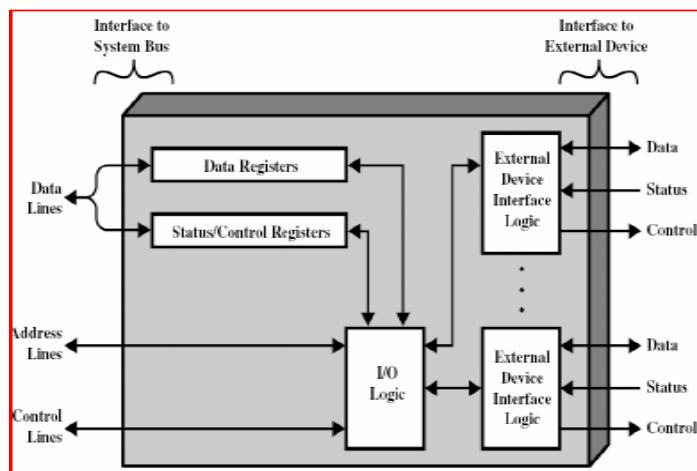

| ● <b>Structure du module d'I/O .....</b>                         | <b>51</b> |

| ● <b>Terminologie .....</b>                                      | <b>52</b> |

| ● <b>Techniques d'entrées/sorties et DMA .....</b>               | <b>52</b> |

|                                                                  |           |

|------------------------------------------------------------------|-----------|

| <b>14. Systèmes d'exploitation. ....</b>                         | <b>52</b> |

| ●Points clés.....                                                | 52        |

| ●Qu'est-ce que c'est qu'un OS ? .....                            | 53        |

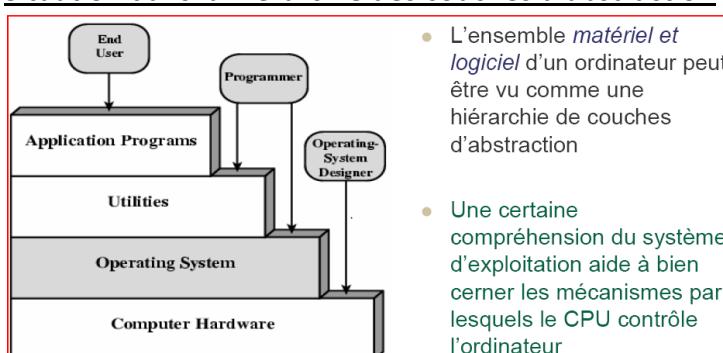

| ●Situation dans la hiérarchie des couches d'abstraction .....    | 53        |

| ●Interface entre utilisateurs et ordinateur .....                | 53        |

| ●Quelques fonctions.....                                         | 54        |

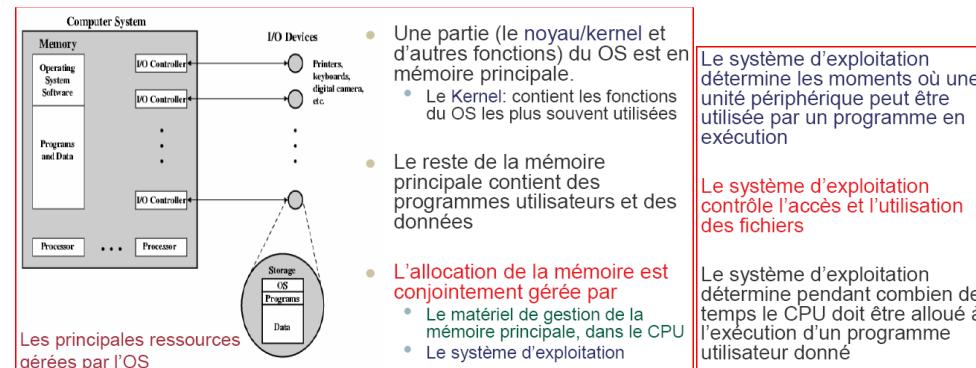

| ●Gestionnaire des ressources .....                               | 54        |

| ●Type – classification suivant deux dimensions.....              | 54        |

| ●Les tous premiers ordinateurs .....                             | 55        |

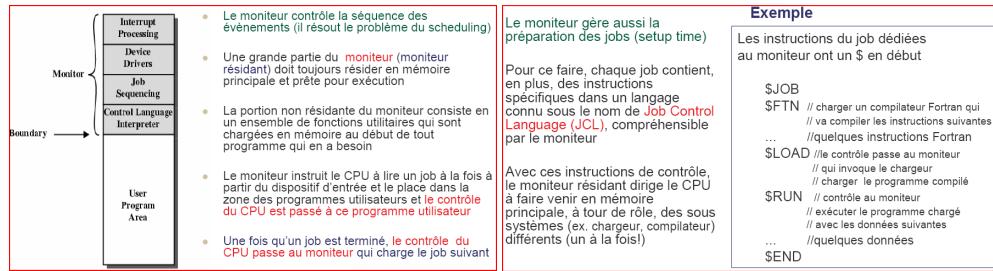

| ●Les systèmes batch simples .....                                | 55        |

| ○ Observation .....                                              | 56        |

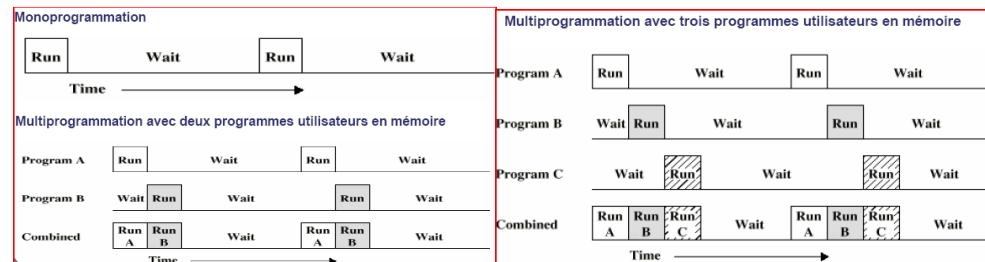

| ○ Mauvaise exploitation du CPU illustrée .....                   | 57        |

| ●Les systèmes batch multiprogrammés.....                         | 57        |

| ●Temps partagés ( <i>time sharing</i> ) .....                    | 58        |

| ●Différences entre batch multiprogrammés et temps partagés ..... | 58        |

| ●Concept de processus .....                                      | 58        |

| ●Le scheduling .....                                             | 59        |

| ●Le Process Control Bloc.....                                    | 60        |

| ●Gestion de la mémoire .....                                     | 61        |

| ●Mémoire virtuelle.....                                          | 61        |

| ○ Idée de base .....                                             | 61        |

| ○ Avantages .....                                                | 61        |

| <b>15. Arithmétiques des ordinateurs.....</b>                    | <b>61</b> |

## **Fonctionnement des Ordinateurs – Examen 08.**

### **1. Introduction aux ordinateurs.**

#### **Définition : Architecture des ordinateurs.**

Aspects logiques, attributs de l'ordinateur visibles au programmeur en langage machine. Les aspects architecturaux ont donc un impact direct sur l'exécution des programmes. (Ex : adressage de la mémoire, représentation de chaque type de données,...)

#### **Définition : Organisation des ordinateurs.**

Aspects physiques, unités opérationnelles et leurs interconnexions qui réalisent l'architecture c à d comment sont implémentées les caractéristiques. (Ex : technologie utilisée pour la mémoire, le nombre de registres utilisés,...)

Une architecture correspond à plusieurs organisations, en effet l'architecture est une spécification qui peut durer quelques temps alors que l'organisation est une implémentation qui varie selon les technologies.

#### **Fonctions de base d'un ordinateur.**

Elles sont au nombre de 4 :

- Traitement des données

- Déplacement des données

- Mémorisation des données

- Lecture

Les données sont transférées de l'environnement vers la mémoire.

- Ecriture

Les données sont transférées de la mémoire vers l'environnement.

- Mémorisation temporaire

Les données en cours de traitement.

- Mémorisation à long terme

Sauvegarde des données pour utilisation ultérieure.

- Contrôle des 3 autres fonctions

#### **Structure interne d'un ordinateur.**

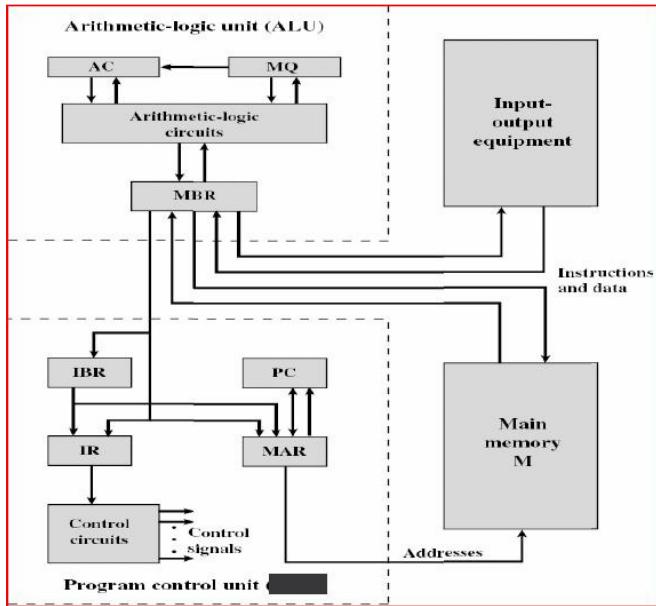

##### **1. Processeur – CPU (Central Processing Unit)**

- Le cœur de l'ordinateur, il contrôle le fonctionnement de l'ordinateur et exécute les (instructions) fonctions de traitement des données.

- Unité de contrôle qui contrôle le fonctionnement du CPU et donc de l'ordinateur.

- Unité Arithmétique et Logique (ALU) qui effectue les fonctions de traitements des données

- Les registres qui sont la mémoire interne du CPU

- L'interconnexion du processeur qui gère la communication entre les 3 composants ci-haut.

## **2. Mémoire principale**

- Dispositif de mémorisation des données en cours de traitement.

## **3. Entrées/Sorties (E/S ou I/O)**

- Transfert des données entre l'ordinateur et son environnement.

## **4. Interconnexion des systèmes**

- Gère la communication entre le CPU, la mémoire et les E/S.

## **Evolution et performances des ordinateurs.**

- Caractéristiques de l'évolution des ordinateurs :

- ✓ Augmentation de la vitesse des CPU

- ✓ Diminution de la taille des ordinateurs

- ✓ Augmentation de la taille des mémoires

- ✓ Augmentation de la capacité et vitesse des E/S

- Facteurs responsables de l'augmentation de la vitesse des processeurs :

- ✓ Diminution de la taille des microprocesseurs → *La réduction de la distance entre les composants conduit à une augmentation de la vitesse.*

- ✓ Organisation du CPU → Utilisation de techniques comme « *Le pipelining* », « *l'exécution parallèle* » et « *l'exécution spéculative* » afin de **maintenir le CPU actif presque tout le temps.**

Dans la conception d'un ordinateur, il est très difficile de trouver un équilibre entre les performances des différents composants. En effet, la vitesse du CPU ayant été considérablement augmentée, le temps d'accès à la mémoire ne suit pas. On utilise alors des techniques telles que *la mémoire cache*, *large chemin de données entre CPU et la mémoire* et *des puces mémoires plus sophistiquées* pour compenser le déséquilibre.

## **2. Première génération d'ordinateurs.**

Ils étaient construits sur la technologie des tubes à vide, ils étaient très volumineux et consommaient beaucoup d'énergie.

### **1. ENIAC**

Premier ordinateur électronique numérique généraliste, conçu et construit à l'université de Pennsylvanie par le professeur *John Mauchly* et le doctorant *John Presper Eckert* dans le but de venir en aide aux américains pour la seconde guerre mondiale. Il avait pour objectif de faire des calculs pour le laboratoire de balistique mais, bien que sa construction ait commencé en 1943, il ne fut pas achevé avant 1946 et donc il ne fut pas utilisé pour la guerre. Cependant il fut tout de même utilisé jusqu'en 1955.

- Caractéristiques :

- Poids : 30 Tonnes.

- 5000 Additions/seconde.

- 18000 tubes à vide.

- 140 kilowatts de consommation électrique

- Arithmétique en base 10, chaque chiffre étant représenté par un anneau de 10 tubes à vide.

- Programmé manuellement → Positionnement des commutateurs, brancher et débrancher des câbles **manuellement**. Ceci était un **inconvénient majeur**.

## 2. IAS (Machine de Von Neumann)

Conçu dans l'optique de pallier à la grande difficulté de programmer l'ENIAC. L'idée essentielle est de mettre le programme et les données dans une mémoire centrale, c'est le concept de programme enregistré (*stored-program concept*). Sa construction a été lancée en 1946 et s'est terminée en 1952, et cette machine sert de prototype pour tous les ordinateurs à usage général.

- Caractéristiques :

- Une mémoire principale qui contient des instructions machines et des données.

- Une unité arithmétique et logique (ALU) qui effectue les opérations sur des données binaires (addition, soustraction, multiplication et division)

- Une unité de contrôle qui interprète les instructions en mémoire et cause leur exécution

- Un dispositif d'entrées/sorties qui est géré par l'unité de contrôle et qui échange des données avec les périphériques.

Définition : Un **mot mémoire** est une unité d'informations accessible en une seule opération de lecture.

Pour l'IAS, la mémoire consistait en 1000 mots de 40 bits chacun.

### 2 types de mots :

Mots de type « donnée » (nombre)

Mots de type « instruction » : 2 instructions de 20 Bits avec un *code op* qui indique l'opération à effectuer suivi d'une adresse indiquant un des mots mémoire.

### Fonctionnement de l'IAS.

L'unité de contrôle fait fonctionner l'IAS en causant l'extraction des instructions de la mémoire et l'exécution de ces instructions une à la fois.

On peut découvrir l'existence d'unité de mémorisation à l'intérieur du CPU, ce sont les **registres**. Il y a les registres de l'ALU et les registres de l'unité de contrôle.

- ✖ **AC (Accumulator)** et **MQ (Multiplier and Quotient)** : Ils sont utilisés pour stocker temporairement des opérandes et des résultats (bits les plus significatifs) des opérations de l'ALU.

- ✖ **MBR (Memory Buffer Register)** est utilisé pour stocker un mot mémoire devant être transféré en mémoire ou pour recevoir un mot mémoire venant de la mémoire.

- ✖ **MAR (Memory Address Register)** spécifie l'adresse du mot mémoire dans lequel on va mettre le contenu du **MBR** (**écriture**) ou à partir duquel on va extraire le contenu à mettre dans le **MBR** (**lecture**).

- ✖ **IR (Instruction Register)** est utilisé pour stocker le code en 8bits de l'instruction en cours d'exécution.

- ✖ **IBR (Instruction Buffer Register)** est utilisé pour stocker temporairement l'instruction de droite d'un mot mémoire.

- ✖ **PC (Program Counter)** est utilisé pour stocker l'adresse de la prochaine paire d'instructions à extraire de la mémoire.

Le fonctionnement se fait par cycle d'instruction répété, chaque cycle consistant en 2 sous-cycles : la **lecture** et l'**écriture**.

## Cycle d'instruction de l'IAS

### Sous-cycle de lecture

- 1. La prochaine instruction est-elle dans le IBR?

- 2. **Oui** (dans ce cas, pas d'accès mémoire)

- 2.1.  $IR \leftarrow IBR(0:7)$

- i.e. code op est chargé dans IR

- 2.2.  $MAR \leftarrow IBR(8:19)$

- i.e. l'adresse correspondante est chargée dans MAR

- 2.3.  $PC \leftarrow PC + 1$

- i.e. on incrémente le PC

- passer au cycle d'exécution de l'instruction dont le code op est dans l'IR

## Cycle d'instruction de l'IAS

### Sous-cycle de lecture

- 1. La prochaine instruction est-elle dans le IBR?

- 3. **Non** (dans ce cas, il faut aller en mémoire)

- 3.1.  $MAR \leftarrow PC$

- i.e. compteur de programme est mis dans MAR

- 3.2.  $MBR \leftarrow M(MAR)$

- i.e. le mot mémoire dont l'adresse est dans MAR est mise dans MBR

- 3.4. Faut-il utiliser l'instruction de gauche?

- 3.5. **Non**

- 3.5.1.  $IR \leftarrow MBR(20:27)$

- 3.5.2.  $MAR \leftarrow MBR(28:39)$

- 3.5.3.  $PC \leftarrow PC + 1$

- Passer au cycle d'exécution dont le code op est dans IR

## Cycle d'instruction de l'IAS

### Sous-cycle de lecture

- 1. La prochaine instruction est-elle dans le IBR?

- 3. **Non** (dans ce cas, il faut aller en mémoire)

- ...

- 3.4. Faut-il utiliser l'instruction de gauche?

- 3.6. **Oui**

- 3.6.1.  $IBR \leftarrow MBR(20:39)$

- 3.6.2.  $IR \leftarrow MBR(0:7)$

- 3.6.3.  $MAR \leftarrow MBR(8:19)$

- passer au cycle d'exécution dont le code op est dans le IR

## Cycle d'instruction de l'IAS

### Sous-cycle de lecture

#### Note:

- Pendant le sous-cycle de lecture, le code de la prochaine instruction est chargée dans le RI

- L'adresse est chargée dans le MAR

- L'instruction à charger dans IR peut être obtenue de deux façons:

- A partir du IBR, ou

- A partir de la mémoire via MBR, IBR, IR et MAR

### Sous-cycle d'exécution.

Le code op, maintenant dans l'**IR**, est interprété et exécuté par les circuits de contrôle. L'exécution de l'instruction par les circuits de contrôle génère des **signaux de contrôle** particuliers qui provoquent une certaine action : **Mouvement des données** ou **Traitements des données** (*exécution d'une opération*) par l'**ALU**.

Il y avait 21 instructions de l'**IAS** regroupées en 5 catégories :

- ♠ **Transfert de données** : Déplacement des données entre la mémoire et les registres de l'**ALU** ou entre deux registres de l'**ALU**.

- ♠ **Branchement inconditionnel** : Modifier le contenu du **PC** pour faire des branchements (exemple : répétitions)

- ♠ **Branchement conditionnel** : Modifier le contenu du **PC** sur base d'une condition → Points de décisions.

- ♠ **Arithmétiques** : Opérations sur des données, exécutées par l'**ALU**.

- ♠ **Modification d'adresse** : Permet de calculer des adresses dans l'**ALU**, puis de les insérer dans des instructions rangées en mémoire. Similaire aux tableaux indexés.

### **3. Deuxième génération d'ordinateurs.**

**Définition** : Un transistor est un composant solide en silicium inventé en 1947 dans les laboratoires Bell. Il est plus petit par rapport aux tubes à vide et il réduit la consommation d'énergie.

Cette génération est basée sur les transistors. Les unités arithmétiques et logiques sont plus complexes, on introduit les langages de haut niveau et les logiciels système.

### **4. Troisième génération d'ordinateurs.**

Basée sur la micro-électronique → Les circuits intégrés.

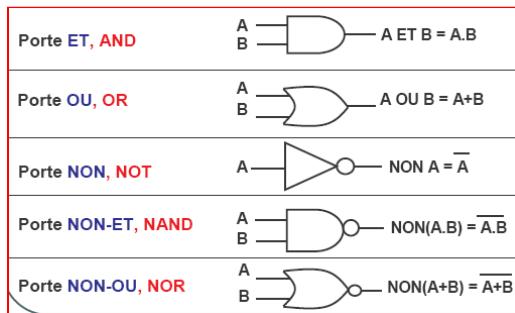

Les éléments fondamentaux de l'ordinateur sont les portes et les cellules de mémoires.

**Définition** : Une **porte logique** est un composant capable de mettre en œuvre une fonction booléenne ou logique simple. (On les appelle portes car elles fonctionnent de la même manière d'une écluse.) C'est un circuit électrique qui produit un signal de sortie sous forme d'une opération booléenne sur ses signaux d'entrée. Chaque porte possède une ou plusieurs (souvent 2) entrées et une sortie. Un changement de données à l'entrée entraîne presque instantanément la sortie correcte.

Un jeu de portes est dit fonctionnellement complet s'il permet d'implémenter n'importe quelle fonction booléenne. De telle façon, on simplifie la conception et la fabrication des circuits car on se limite à un ou 2 types de portes. Les circuits numériques sont souvent implémentés uniquement avec des portes NON-ET ou uniquement avec des portes NON-OU.

**Définition** : Une **cellule de mémoire** est un composant capable de mémoriser un bit de donnée.

Lien entre éléments de bases et les 4 fonctions d'un ordinateur → voir transparents.

## Conception pour la performance.

Du point de vue de l'organisation et de l'architecture des ordinateurs, 2 aspects sont frappants : les blocs de base des ordinateurs d'aujourd'hui sont les mêmes que ceux de l'**IAS** et les techniques d'amélioration des performances du matériel sont de plus en plus sophistiquées.

## Vitesse des microprocesseurs.

Les puces de mémoire ont quadruplé tous les trois ans la capacité des mémoires dynamiques à accès aléatoire (**DRAM**, *Dynamic Random Access Memory*), qui forme la technologie de base des mémoires principales d'ordinateurs.

Les microprocesseurs contemporains sont caractérisés par une grande vitesse, qui découle de la réduction des distances entre composants fondamentaux. Il faut donc des techniques appropriées pour maintenir le microprocesseur constamment occupé pour ainsi exploiter toute la puissance brute des processeurs. Voici quelques-unes de ces techniques :

### ≈ **Prédiction des branchements**

Le processeur essaie de trouver, sur base de l'instruction courante, les branchements ou les groupes d'instructions à exécuter dans la suite.

### ≈ **Analyse des flots de données**

Le processeur essaie de créer un ordonnancement optimisé des instructions, en analysant les instructions qui sont dépendantes des résultats d'autres instructions. Ceci évite des attentes inutiles.

### ≈ **Exécution spéculative**

Exécution anticipée des instructions avant qu'elles n'apparaissent réellement dans l'exécution du programme. Les résultats de telles exécutions sont mis dans des emplacements temporaires.

### ≈ **Pipelining**

Subdiviser le cycle d'instruction en tâches et exécuter ces tâches en parallèle. (Ex : lire la prochaine instruction en parallèle avec l'exécution de celle en cours.)

### ≈ **Superscalaire**

Formation d'un flot d'exécution dynamique, grâce à l'utilisation de la prédiction de branchement. Le processeur analyse ce flot afin de déterminer des dépendances des données et élimination des dépendances artificielles. ➔ Exécution des instructions suivant les vraies dépendances.

- Les processeurs et la capacité des mémoires a augmenté très rapidement mais la vitesse de transfert entre la mémoire centrale et le processeur augmente très lentement. C'est donc le chemin le plus critique de l'ordinateur.

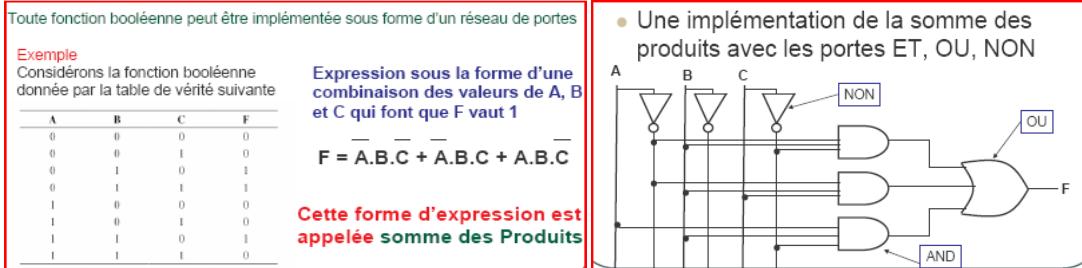

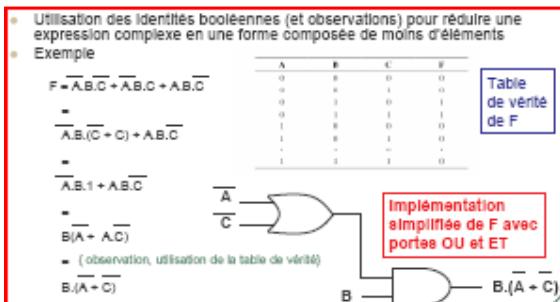

## Les circuits combinatoires.

**Définition :** Ensemble de portes interconnectées dont la valeur de sortie à un instant donné ne dépend que des valeurs d'entrée à cet instant. Il se compose de n entrées binaires et de m sorties binaires. On peut les définir de 3 manières, en donnant la table de vérité, les symboles graphiques ou une équation booléenne.

**Exemple :**

D'où l'intérêt de simplifier les expressions booléennes afin d'utiliser peu de portes pour l'implémentation.

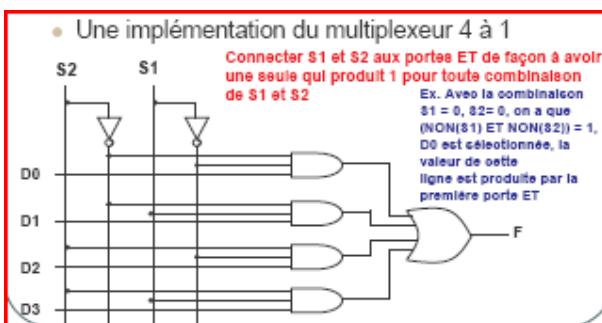

## Multiplexeurs.

Ce sont des circuits combinatoires connectant plusieurs entrées à une seule sortie : à chaque moment, une seule entrée est sélectionnée pour être passée à la sortie. Il permet de transmettre sur une même ligne (sortie) des informations provenant de plusieurs sources (entrées).

## Décodeurs.

Circuit combinatoire ayant n entrées et  $2^n$  sorties, en fonction de la chaîne de bits en entrée, une seule des  $2^n$  lignes de sorties est sélectionnée.

- Décodeur avec 3 entrées et 8 sorties

| Entrée |   |   | Sortie |    |    |    |    |    |    |    |

|--------|---|---|--------|----|----|----|----|----|----|----|

| A      | B | C | D0     | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

| 0      | 0 | 0 | 1      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0      | 0 | 1 | 0      | 1  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0      | 1 | 0 | 0      | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 0      | 1 | 1 | 0      | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| 1      | 0 | 0 | 0      | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

| 1      | 0 | 1 | 0      | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 1      | 1 | 0 | 0      | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 1      | 1 | 1 | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

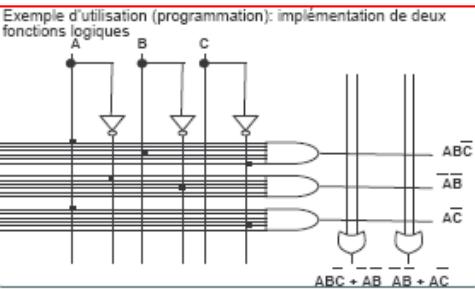

## Tableaux logiques programmables.

L'objectif est de développer une puce à usage général adaptable à des objectifs spécifiques, le principe est fondé sur le fait que toute fonction booléenne peut être exprimée sous la forme d'une somme de produits.

Ils sont souvent appelés des circuits sans mémoires parce que la sortie d'un circuit combinatoire dépend uniquement de l'entrée en cours et donc il n'y a pas de mémorisation de l'histoire des entrées précédentes.

## 5. Conversion binaire-décimal-hexadécimal.

- Binaire → Décimal.

... $b_2 b_1 b_0, b_{-1} b_{-2} b_{-3}$ ... un nombre binaire. Alors la valeur de ce nombre en base décimale est :  $(\sum_i b_i \cdot 2^i)_{10}$  autrement dit, il faut multiplier chaque 0 ou 1 par  $2^{position}$ .

- Décimal → Binaire.

Succession de divisions du nombre décimal par 2 et on note le reste à l'envers. (Conversion de la partie entière)

Exemple : 11,  $11/2 = 5$  (+1) ;  $5/2 = 2$  (+1) ;  $2/2 = 1$  (+0) ;  $1/2 = 0$  (+1) →  $(11)_{10} = (1011)_2$ .

Conversion de la partie fractionnaire. Succession de multiplication du nombre décimal par 2 et on note le nombre entier obtenu et on garde la partie fractionnaire.

Exemple : **0,35** ;  $0,35 \cdot 2 = 0,7$  ;  $0,7 \cdot 2 = 1,4$  ;  $0,4 \cdot 2 = 0,8$  ;  $0,8 \cdot 2 = 1,6$  ;  $0,6 \cdot 2 = 1,2$  ;  $0,2 \cdot 2 = 0,4$  on cycle !  $\Rightarrow (0,35)_{10} = (0,010110)_2$

- Hexadécimal  $\Rightarrow$  Décimal.

$1=1$  ;  $2=2$  ...  $9=9$  ;  $A=10$  ;  $B=11$  ;  $C=12$  ;  $D=13$  ;  $E=14$  ;  $F=15$ .

$$\begin{aligned}\Rightarrow (8EA)_{16} &= (8 \cdot 16^2 + E \cdot 16^1 A \cdot 16^0)_{10} = (8.256 + 14.16 + 10.1)_{10} \\ \Rightarrow &= (2048 + 224 + 10)_{10} = (2282)_{10}\end{aligned}$$

- Binaire  $\Rightarrow$  Hexadécimal.

On organise le nombre binaire à convertir en groupes de 4 bits et on remplace chaque groupe par sa valeur en Hexadécimal.

|          |          |

|----------|----------|

| 0000 = 0 | 1000 = 8 |

| 0001 = 1 | 1001 = 9 |

| 0010 = 2 | 1010 = A |

| 0011 = 3 | 1011 = B |

| 0100 = 4 | 1100 = C |

| 0101 = 5 | 1101 = D |

| 0110 = 6 | 1110 = E |

| 0111 = 7 | 1111 = F |

## 6. La mémoire à lecture seulement.

### Définition

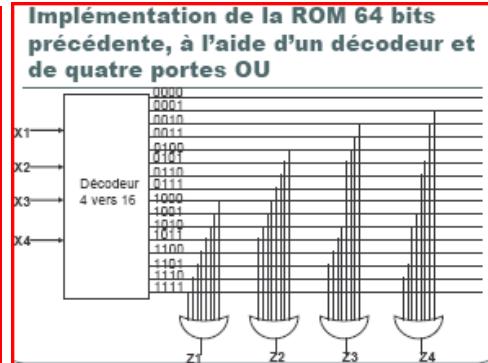

La *Read-Only Memory*, la ROM, est une mémoire implémentée par des circuits combinatoires. C'est une mémoire qui ne supporte que l'opération de lecture, les informations binaires dans la ROM sont permanentes et son stockées pendant la fabrication du circuit donc une entrée produit toujours la même sortie (donnée), elle peut être implémentée avec un décodeur et des portes OU.

| Mémoire morte:            |         |

|---------------------------|---------|

| Table de vérité d'une ROM |         |

| Entrée                    | Sortie  |

| 0 0 0 0                   | 0 0 0 0 |

| 0 0 0 1                   | 0 0 0 1 |

| 0 0 1 0                   | 0 0 1 1 |

| 0 0 1 1                   | 0 0 1 0 |

| 0 1 0 0                   | 0 1 1 0 |

| 0 1 0 1                   | 0 1 1 1 |

| 0 1 1 0                   | 0 1 0 1 |

| 0 1 1 1                   | 0 1 0 0 |

| 1 0 0 0                   | 1 1 0 0 |

| 1 0 0 1                   | 1 1 0 1 |

| 1 0 1 0                   | 1 1 1 0 |

| 1 0 1 1                   | 1 1 1 1 |

| 1 1 0 0                   | 1 0 1 0 |

| 1 1 0 1                   | 1 0 1 1 |

| 1 1 1 0                   | 1 0 0 1 |

| 1 1 1 1                   | 1 0 0 0 |

| 1 1 1 1                   | 1 0 0 0 |

Peut être vu comme le contenu d'une ROM de 64 bits composée de 16 mots de 4 bits chacun

Les quatre entrées: spécifient une adresse

Les quatre sorties: spécifient le contenu de l'emplacement mémoire désigné

## Le problème des additionneurs.

### ● Additionneur mono-bit

- Additionne deux bits d'entrée

- Produit

- Un bit de somme

- Un bit de retenue

| A | B | Somme | Retenue |

|---|---|-------|---------|

| 0 | 0 | 0     | 0       |

| 0 | 1 | 1     | 0       |

| 1 | 0 | 1     | 0       |

| 1 | 1 | 0     | 1       |

Traitement de l'addition binaire en termes booléens

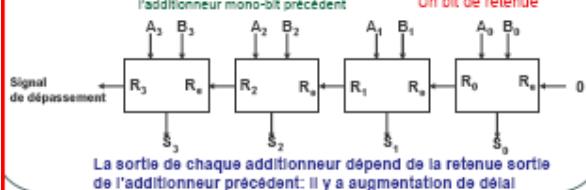

### ● Additionneur multi-bits

- Peut être construit sur des additionneurs mono-bit

- Chaque additionneur mono-bit doit avoir

Trois entrées:

- Deux bits du niveau courant

- Un bit de retenue provenant de l'additionneur mono-bit précédent

Deux sorties:

- Un bit de somme

- Un bit de retenue

La sortie de chaque additionneur dépend de la retenue sortie de l'additionneur précédent: Il y a augmentation de délai!

### ● Table de vérité révisée de l'addition

| R <sub>entrée</sub> | A | B | Somme | R <sub>sortie</sub> |

|---------------------|---|---|-------|---------------------|

| 0                   | 0 | 0 | 0     | 0                   |

| 0                   | 0 | 1 | 1     | 0                   |

| 0                   | 1 | 0 | 1     | 0                   |

| 0                   | 1 | 1 | 0     | 1                   |

| 1                   | 0 | 0 | 1     | 0                   |

| 1                   | 0 | 1 | 0     | 1                   |

| 1                   | 1 | 0 | 0     | 1                   |

| 1                   | 1 | 1 | 1     | 1                   |

$$\text{Somme} = \overline{A}\overline{B}C + \overline{A}B\overline{C} + ABC + A\overline{B}\overline{C}$$

$$\text{Retenue (sortie)} = AB + AC + BC$$

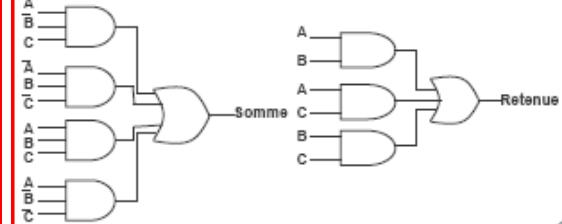

### ● Implémentation d'un additionneur avec des portes ET et OU

La construction basée sur des additionneurs mono-bits est limitée par l'accumulation des délais de propagation. La solution est de construire des additionneurs de plus de 1 bit, par exemple construire sur des additionneurs de 8 bits.

## 7. Circuits séquentiels.

Les circuits combinatoires (à l'exception de la ROM) n'offrent pas de mémoire ou d'informations d'état, on utilise les circuits séquentiels.

### ● Définition

C'est une forme plus complexe de circuit logique numérique utilisée pour servir de mémoire. La sortie d'un tel circuit dépend de l'entrée en cours et de son état courant. Exemple : Les bascules, les registres, les compteurs.

### ● Les bascules.

Une bascule a deux états. Elle se trouve à tout moment dans l'un ou l'autre des 2 états. En l'absence d'entrée, elle reste dans son état courant. Une bascule a 2 sorties, qui sont toujours le complément l'une de l'autre. Ces sorties sont généralement libellées  $Q$  et  $\overline{Q}$ . Une bascule peut servir comme mémoire à 1 bit.

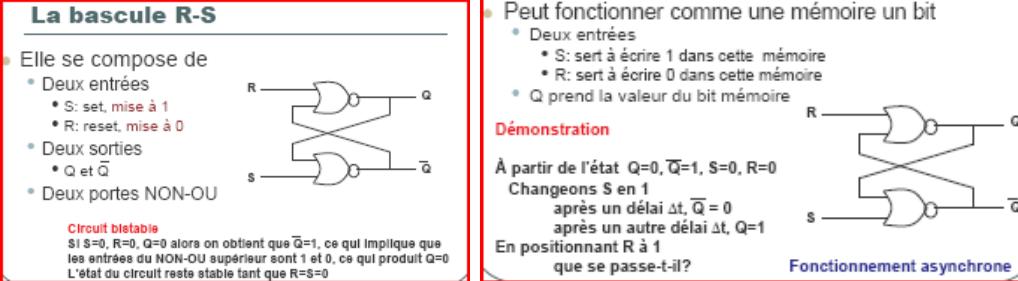

## o La bascule R-S

Table caractéristique

- Montre le ou les prochains états d'un circuit séquentiel sous forme d'une fonction des états et des entrées en cours

| Entrées en cours | Etat en cours | Etat suivant |

|------------------|---------------|--------------|

| SR               | $Q_n$         | $Q_{n+1}$    |

| 00               | 0             | 0            |

| 00               | 1             | 1            |

| 01               | 0             | 0            |

| 01               | 1             | 0            |

| 10               | 0             | 1            |

| 10               | 1             | 1            |

| 11               | 0             | -            |

| 11               | 1             | -            |

**Note**

L'entrée  $S=R=1$

n'est pas autorisée

Car résultat illégal

La bascule R-S a un fonctionnement asynchrone : sa sortie change, après un court délai, en réponse à un changement de l'entrée.

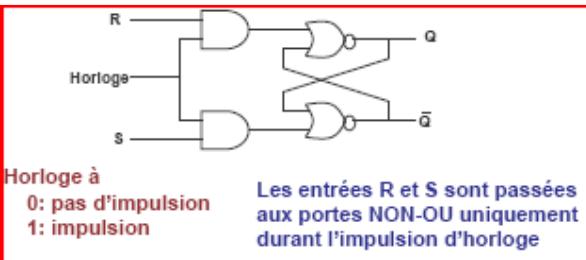

## o La bascule R-S avec horloge

Dans un ordinateur, les événements sont en général synchronisés par une impulsion horloge. Les changements se produisent uniquement au moment de l'impulsion d'horloge. La **bascule R-S avec horloge** permet de mettre en œuvre ce fonctionnement où les changements sont contraints par l'impulsion horloge.

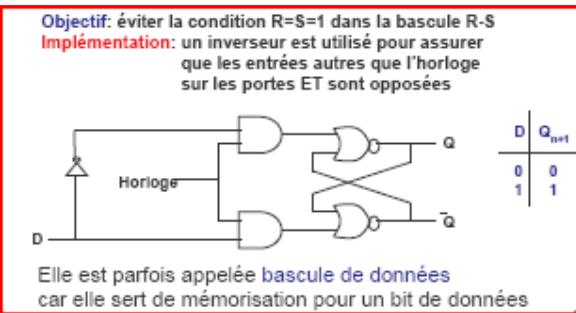

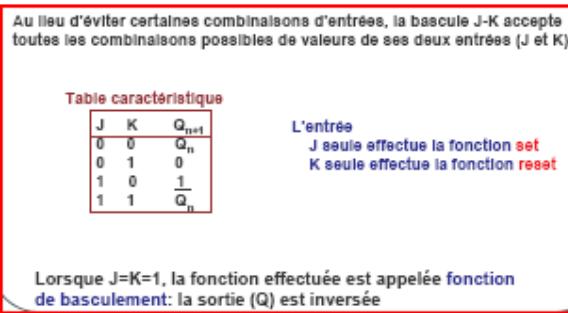

- La bascule D

- La bascule J-K

- Les registres.

**Définition:** C'est un des éléments les plus essentiels du **CPU**, c'est un circuit digital utilisé dans le **CPU** pour stocker un ou plusieurs bits de données. Ils illustrent l'utilisation des bascules.

Il y a 2 types de registres :

✓ **Les registres parallèles.**

Ils sont composés d'une série de mémoires 1bit (bascules) que l'on peut lire ou écrire simultanément. Ils servent à ranger (stocker) des données.

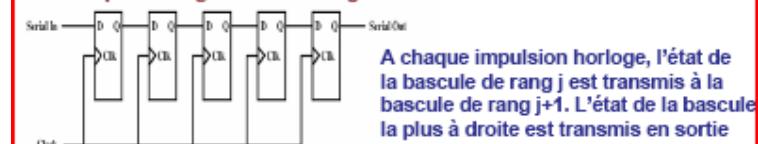

✓ **Les registres à décalage.**

C'est un registre qui accepte et/ou transfère des informations en série. Ils peuvent être utilisés pour interfaçer des dispositifs d'entrées/sorties sériels et dans l'**ALU** pour des opérations de décalage et de rotation logique.

**Exemple de registre à décalage construit avec des bascules D**

- Les compteurs.

Définition: C'est un registre (série de bascules) dont la valeur (contenu) est facilement incrémentée de 1 modulo sa capacité. Un registre compteur de  $n$  bits pour ainsi compter jusqu'à  $2^n - 1$

Exemple : le **PC** dans le **CPU**.

- Compteur asynchrone (ou en cascade).

Les bascules qui le composent changent d'état à des moments différents (propagation du changement d'une extrémité à l'autre)

- Compteur synchrone.

Toutes les bascules changent d'état au même moment. Il est plus rapide que le compteur asynchrone, il est utilisé dans les **CPU**.

## **8. Programmation matérielle et programmation logicielle.**

Des composants logiques de base peuvent être interconnectés pour stocker des données binaires et pour effectuer des opérations arithmétiques et logiques sur ces données.

- **Programmation matérielle.**

Pour un problème donné, on doit :

- ✓ trouver une configuration des composants logiques de base spécifiques,

- ✓ réaliser l'interconnexion de ces composants,

Le processus de réalisation de l'interconnexion est une forme de programmation. Le programme qui en résulte est connu sous le nom de **programme câblé (hardwired program)**.

➔ Une modification du programme implique un re-câblage ➔ Approche fort limitée.

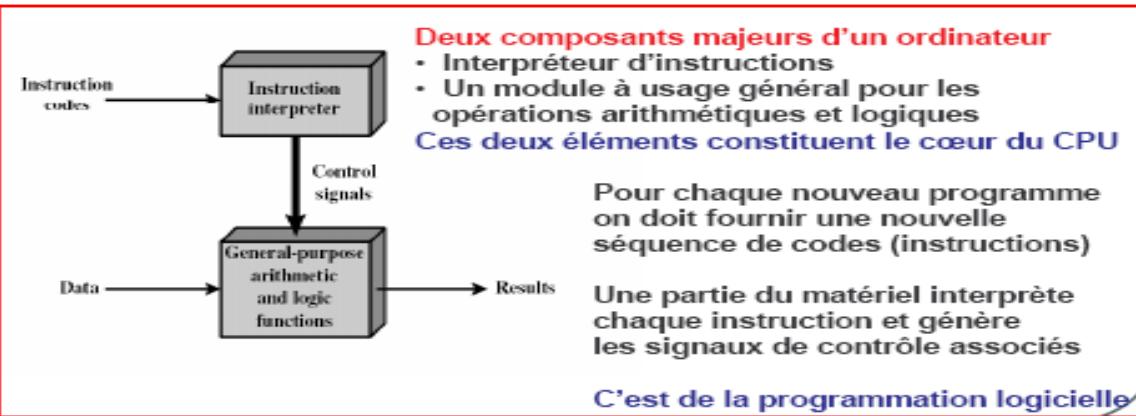

- **Programmation logicielle.**

Se base sur l'idée d'une configuration matérielle à usage général, pouvant effectuer des opérations arithmétiques et logiques. Cette configuration opère sur base des signaux de contrôle qui lui sont envoyés. Le programmeur n'a donc plus à re-câbler pour chaque nouveau programme, il a juste besoin de fournir de nouveaux signaux de contrôle.

### **Comment fournir ces signaux à ce dispositif matériel à usage général ?**

Rappelons nous, un programme est une séquence de pas (instructions), à chaque pas, une opération est effectuée sur des données. Pour chaque pas, un nouvel ensemble de signaux de contrôle est nécessaire.

L'astuce réside en un code pour chaque ensemble de signaux de contrôle possible et un dispositif capable d'accepter un code et générer des signaux de contrôle correspondants.

*Cycle d'instruction/exécution/interruptions..... → Transparents.*

## 9. Structures d'interconnexion.

Un ordinateur consiste en un ensemble de composants ou modules de trois types de base :

- Processeur

- Mémoire

- Module d'I/O

qui communiquent entre eux.

La collection des chemins qui interconnectent ces modules forme ce que l'on appelle **structure d'interconnexion**. La conception de cette structure dépend des échanges devant s'effectuer entre ces modules.

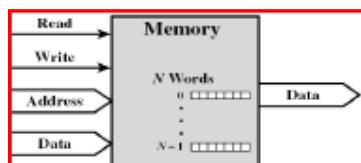

- Le module mémoire.

En général, un module mémoire consiste en **N mots (words)** de même longueur. Chaque mot possédant comme adresse un numéro pris dans  $\{0,1,\dots,N-1\}$ . Un mot mémoire de données peut être lu ou écrit dans la mémoire, la nature de l'opération étant indiquée par un signal de contrôle et l'emplacement de la mémoire où lire ou écrire est indiqué par une adresse.

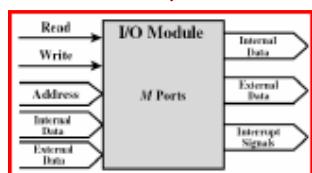

- Le module d'I/O.

Vu de l'intérieur de l'ordinateur, un module d'I/O fonctionne comme un module mémoire (*Il y a 2 opérations : Lecture et Ecriture*). De plus un module d'I/O peut contrôler plus d'une unité périphérique. On peut désigner par un [port](#), chacune des interfaces vers les unités périphériques, dès lors on peut donner à chaque port un numéro unique  $\in \{0,1,\dots,M-1\}$  qui est son adresse. De plus, un module d'I/O possède des chemins de données externes pour les entrées/sorties avec l'unité périphérique, il peut également envoyer des signaux d'interruption au processeur.

- **Le processeur.**

Il lit (ou reçoit) des instructions et des données, il écrit des données (résultats), après traitement, en sortie. Il envoie des signaux de contrôle vers d'autres modules pour contrôler le fonctionnement global du système et il reçoit des signaux d'interruptions.

### Les types de transferts supportés

- **Mémoire vers CPU.**

Le **CPU** lit une instruction ou une unité de donnée de la mémoire.

- **CPU vers Mémoire.**

Le **CPU** écrit une unité de donnée dans la mémoire.

- **Module I/O vers CPU**

Le **CPU** lit des données à partir d'une unité périphérique via un **module d'I/O**.

- **CPU vers Module I/O**

Le **CPU** envoie des données à une unité périphérique, via un **module d'I/O**.

- **Entre Module I/O et Mémoire.**

Un **module d'I/O** est autorisé à échanger directement des données avec la **mémoire** sans passer par le **CPU** par l'utilisation de la [Direct Access Memory \(DMA\)](#).

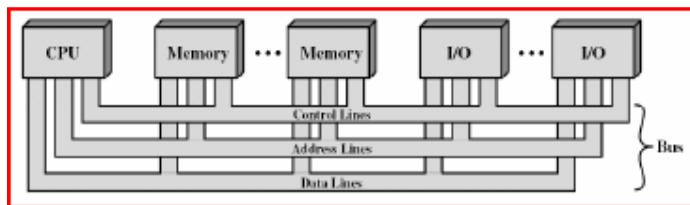

- Interconnexion par [bus](#).

Définition : Un **bus** est un chemin de communication connectant deux ou plusieurs composants, il est partagé par les composants qu'il interconnecte. Un signal envoyé par l'un des composants connectés au bus est recevable par tous les autres composants attachés au bus ([broadcast, diffusion](#)).

Si plusieurs composants connectés au bus émettent en même temps, les signaux sont altérés

➔ **Il faut qu'un seul composant émette à la fois pour garantir une émission avec succès.**

En général, un bus est constitué de plusieurs lignes de communication, chaque ligne étant capable de transmettre des signaux représentant le binaire 1 ou le binaire 0. En envoyant une série de signaux représentant des binaires, on peut transmettre une séquence de bits l'un après l'autre sur une ligne. Plusieurs bits peuvent être transmis simultanément (en parallèle) sur les lignes d'un bus. (Ex : Une unité de données de 8 bits peut être transmise sur un bus 8 lignes.)

Il y a différents bus à différent niveaux de la hiérarchie d'un ordinateur. On appellera **bus système**, un bus qui interconnecte les composants principaux (Processeur, mémoire, module d'I/O) d'un ordinateur. (La grande majorité des structures d'interconnexion utilise un ou plusieurs bus systèmes.) Un bus système, typique, a entre 50 et des centaines de lignes, chaque ligne ayant une signification ou une fonction bien spécifique. En général, ces lignes sont classées en 3 groupes fonctionnels :

- Lignes de données (*bus de données*)

- Lignes d'adresse (*bus d'adresses*)

- Lignes de contrôle (*bus de contrôle*)

On peut aussi avoir des lignes de distribution d'électricité pour alimenter les modules connectés au bus.

- ✓ **Les bus de données** fournissent un chemin permettant de transférer des données entre les modules du système. On appelle **bus de données** l'ensemble des lignes de données, il peut contenir entre 32 et des centaines de lignes.

La largeur du bus de données est égale au nombre de ses lignes, celle-ci détermine combien de bits peuvent être transmis en parallèle (en une fois). **La largeur du bus de donnée est un élément clé dans la performance globale du système.** (Illustration : Si un bus de données a 8 lignes et que chaque instruction a 16 bits, alors le **CPU** doit faire 2 accès mémoire pour chaque cycle d'instruction.)

- ✓ **Le bus d'adresses** est utilisé pour transmettre l'adresse de la source ou de la destination des données se trouvant sur le bus de données. (Ex : pour lire un mot mémoire, le **CPU** place l'adresse du mot qu'il souhaite lire dans le bus d'adresse). **La largeur du bus d'adresses détermine la capacité mémoire maximum, possible, du système.** Les lignes d'adresses sont aussi souvent utilisées pour adresser (désigner) des ports d'I/O.

- ✓ **Utilisation typique du bus d'adresse** : Les bits d'ordre supérieur servent à identifier un module I/O et les bits d'ordre inférieur servent à sélectionner un **emplacement mémoire** ou un **port I/O** dans le **module I/O** identifié avec les bits d'ordre supérieur.

Exemple : Avec un bus d'adresse 8 bits, on pourrait utiliser le bus comme suit :

- Les adresses 00000000...01111111 peuvent référencer des emplacements dans un **module mémoire** (module 0), soit 128 mots mémoires (de l'adresse 0 à 127).

- Les adresses 10000000...11111111 peuvent servir pour identifier les dispositifs connectés à un **module I/O** (module 1).

✓ **Le bus de contrôle** est utilisé pour contrôler l'accès et l'utilisation des bus de données et d'adresse (qui sont partagés par tous les composants qui y sont attachés). Les signaux de contrôle transmettent des **commandes** (*opérations à exécuter*) et des **informations de timing** (*minutage*) entre les modules. Les signaux de timing indiquent la validité des informations sur les bus de données et des adresses.

✓ Quelques commandes typiques des bus de contrôle :

- **Memory write**

Indique que les données sur le bus doivent être écrites en mémoire, à l'adresse indiquée sur le bus d'adresses.

- **Memory read**

Indique que les données se trouvant à l'emplacement dont l'adresse est indiquée sur le bus d'adresses doivent être placées sur le bus de données.

- **I/O write**

Indique que les données se trouvant sur le bus de données soient écrites sur le port I/O indiqué sur le bus d'adresses.

- **I/O read**

Indique que les données se trouvant sur le port I/O indiqué sur le bus d'adresses doivent être placées sur le bus de données.

- **Transfer ACK**

Indique que des données ont été acceptées par (ou placées sur) le bus.

- **Bus request**

Indique qu'un module souhaite avoir le contrôle du bus.

- **Bus grant**

Indique que le contrôle du bus a été accordé à un module demandeur.

- **Interup request**

Indique qu'il y a une interruption en attente.

- **Interup ACK**

Indique que l'interruption en attente a été reconnue.

- **Clock**

Utilisé pour synchroniser les opérations.

- **Reset**

Initialise tous les modules.

- Fonctionnement du bus.

- ♠ Envoi des données.

Lorsqu'un module M<sub>1</sub> souhaite envoyer des données à un autre module M<sub>2</sub>, le module M<sub>1</sub> doit **obtenir le contrôle du bus** et ensuite **transférer les données** via le bus.

♠ Demande des données.

Lorsqu'un module  $M_1$  souhaite demander des données à un autre module  $M_2$ , alors  $M_1$  doit : **obtenir le contrôle du bus, transférer sa requête** (utilisation des lignes de données et d'adresses appropriées) et ensuite **se mettre en attente** des données du module  $M_2$ .

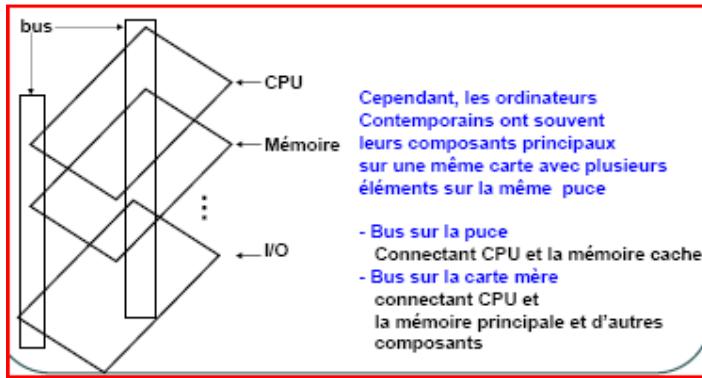

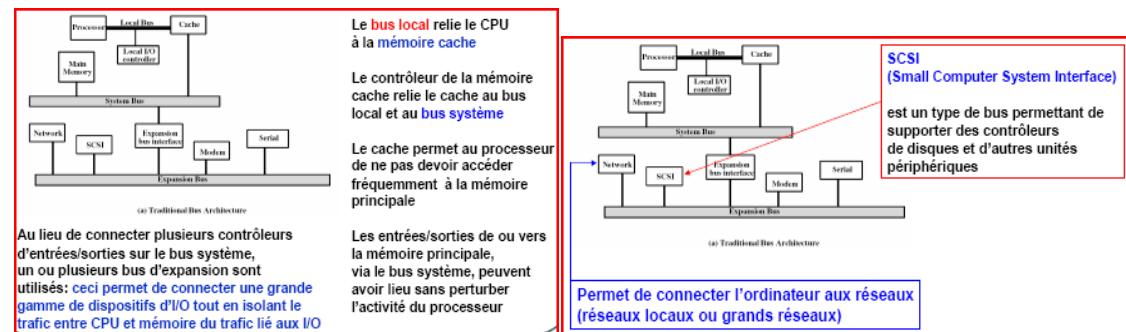

- Réalisation physique typique d'une interconnexion par bus.

Si plusieurs composants sont interconnectés par un seul bus, la performance du système peut être fortement affectée, car plus il y a de composants sur un bus, **plus celui-ci doit être long (ce qui entraîne une augmentation des délais de propagation des signaux)** et **plus il y a de chance** que les demandes cumulées des transferts de données approchent la capacité du bus (*le bus devient alors un goulot d'étranglement, on parle alors de bus bouchonné*).

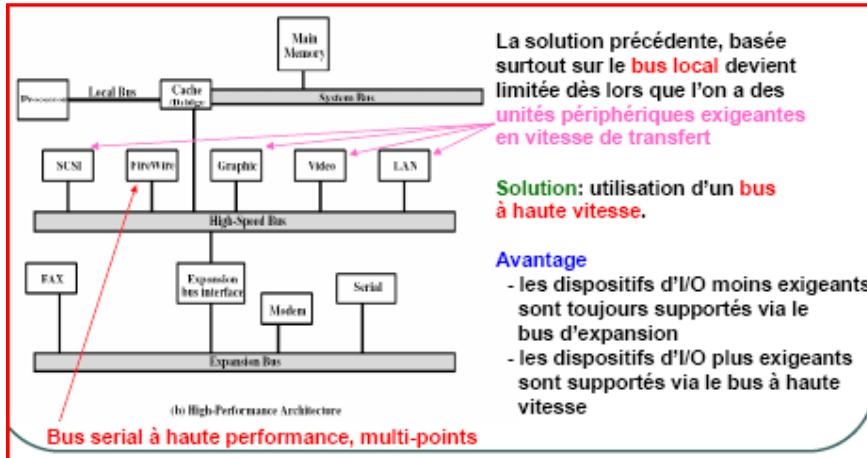

➔ Pour contourner ce problème, la majorité des ordinateurs utilise **plusieurs bus organisés de manière hiérarchique**.

### Le bus local.

## Le bus à haute vitesse.

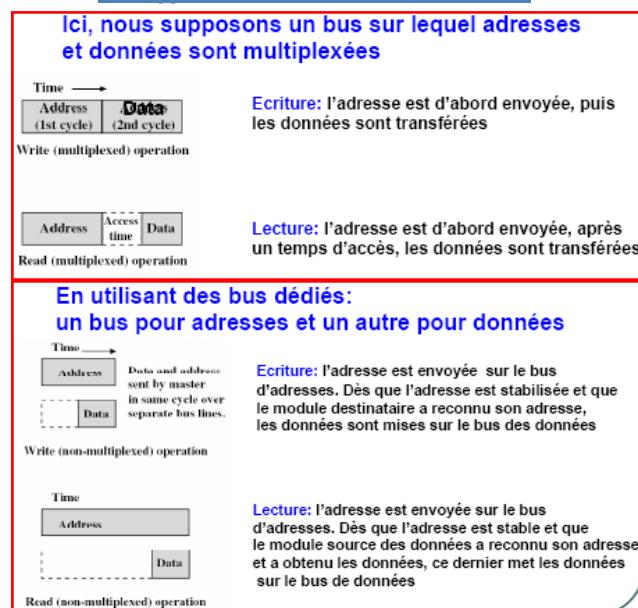

- **Les éléments importants dans la conception de bus :**

- **Le type de bus**

Les lignes d'un bus peuvent être classées en 2 types.

1. **Les lignes dédiées**

Une ligne dédiée est affectée de façon permanente à une fonction ou à un sous-ensemble de composants de l'ordinateur. (**Ex : Lignes dédiées aux adresses et d'autres dédiées aux données**)

2. **Les lignes multiplexées**

Utilisation des mêmes lignes pour par exemple transmettre des adresses et des données. **Multiplexage temporel** :

- Avantage : Implique l'utilisation de moins de lignes → moins d'espace utilisée, coûts réduits.

- Inconvénient : Circuit plus complexes dans des modules, perte de performance potentielle (absence de parallélisme).

- **La méthode d'arbitrage**

Dans la plupart des ordinateurs, plusieurs modules peuvent vouloir le contrôle du bus au même moment mais **un seul module** peut transmettre *avec succès à la fois*. Il faut donc une méthode d'arbitrage. Il y en a **deux** :

- **L'arbitrage centralisé**

Un dispositif matériel, appelé **contrôleur de bus** (*bus controller*), est chargé d'allouer le droit d'accès au bus. Ce contrôleur peut être une **partie du CPU** ou une **unité séparée**.

- **L'arbitrage distribué**

Chaque module possède une logique de contrôle d'accès, ensuite les modules coopèrent afin d'allouer le bus à un seul module à la fois.

- **Le timing**

Le timing d'un bus détermine la manière dont les événements sont coordonnés sur le bus. Il existe 2 types de **timing** :

- Le timing synchrone

Les occurrences des évènements sur le bus sont déterminées par une horloge. Le bus possède alors une ligne horloge via laquelle une horloge transmet une séquence régulière de 1 et de 0 alternés de durée égale et cette ligne peut être lue par tous les autres modules connectés au bus. Une transmission de 1-0 est appelé **cycle horloge** ou **cycl de bus** et détermine un intervalle de temps, tous les évènements commençant **au début d'un cycle horloge**.

- Le timing asynchrone

L'occurrence d'un évènement sur le bus suit et dépend de l'occurrence d'un évènement précédent.

Exemple simplifié : Pour lire un mot mémoire, le processeur va placer l'adresse sur le bus d'adresse et après un lapse de temps il va placer une commande de lecture sur le bus. Le module mémoire va décoder l'adresse mémoire et placer les données demandées sur le bus de données. Après un lapse de temps, le processeur lit les données se trouvant sur la ligne de bus.

- La largeur du bus

La **largeur du bus de données** a un **impact sur la performance globale du système** (*plus le bus de données est large, plus on peut transférer plus de bits en une fois*) et la **largeur du bus d'adresses** a un **impact sur la capacité mémoire du système**.

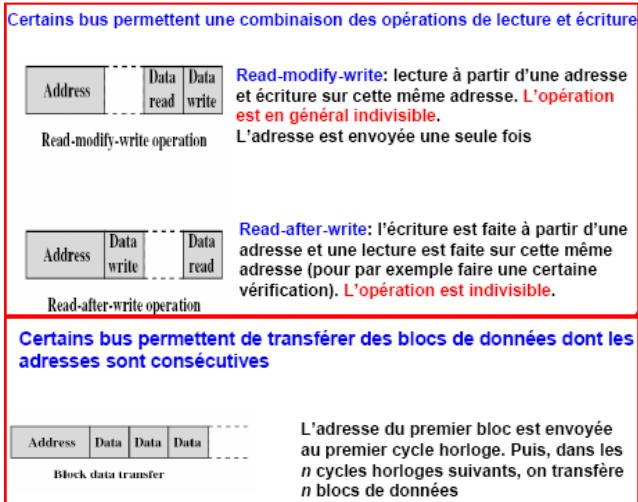

- Les types de transferts de données

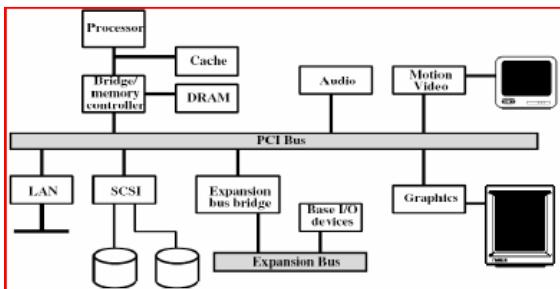

- Le PCI

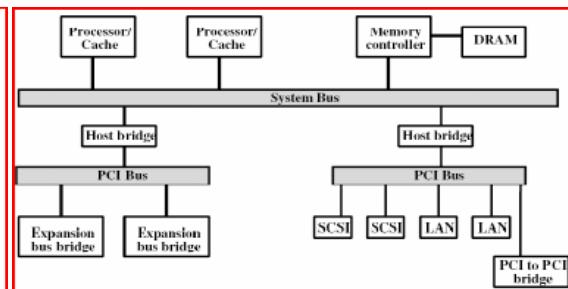

Il s'agit du « *Peripheral Component Interconnect* », c'est un **bus** à haute bande passante, indépendant du processeur, utilisant le **timing synchrone** et la **méthode d'arbitrage centralisée**.

Usages typiques :

Monoprocesseur

Multiprocesseur

## 10. Les mémoires.

- Caractéristiques des mémoires.

Dans un ordinateur, on retrouve des **sous-systèmes de mémorisation** à différents niveaux, par exemple les registres dans le **CPU**, la **mémoire principale** et le **disque dur**. Chaque **sous-système de mémorisation** doit satisfaire des exigences spécifiques, par exemple le temps d'accès par le **CPU** à une donnée se trouvant dans un de ses registres doit être plus court que le temps d'accès à une donnée se trouvant en mémoire principale. En conséquence, il est difficile, si pas impossible, de construire tous les **sous-systèmes de mémorisation** en se basant sur une et une seule technologie donc dans un ordinateur typique, on va retrouver une **hiérarchie de sous-systèmes de mémorisation**.

## Les caractéristiques des mémoires.

### ♠ Emplacement

L'emplacement d'une mémoire est soit interne, soit externe au système.

#### ✓ **Mémoires internes**

Ce sont des mémoires directement accessibles par le **CPU**

Exemple : Registres dans le CPU, Mémoire centrale, Mémoire cache.

#### ✓ **Mémoires externes**

Ce sont des unités périphériques de stockage accessibles via des **modules d'I/O**. Exemple : Disques durs, bandes magnétiques.

### ♠ Capacité

C'est la quantité totale de données pouvant y être stockée

#### ✓ **Mémoires internes**

La capacité est typiquement mesurée en octets ou mots. (*un octet est un groupe de 8 bits et un mot a typiquement 8, 16 ou 32 bits.*)

#### ✓ **Mémoires externes**

La capacité est mesurée en octets (*bytes*).

### ♠ Unité de transfert

Deux notions de base sont liées aux **mémoires internes**,

#### ▪ **Le mot**

C'est l'unité naturelle d'organisation de la mémoire. La taille d'un mot est typiquement égale au nombre de bits utilisé pour représenter un nombre ou à la longueur d'une instruction. (*Le nombre de bits pour représenter un nombre n'étant pas toujours égal au nombre de bits pour une instruction*)

#### ▪ **L'unité adressable**

C'est la plus petite unité de mémoire directement adressable. Si les adresses sont longues de **A bits**, il y a  **$2^A$  unités adressables**. *Dans certains systèmes, l'unité adressable est le mot. Dans d'autres, c'est le byte.*

Pour la **mémoire principale**, c'est le nombre de bits lus(ou écrits) simultanément. *L'unité de transfert n'est pas forcément égale à un mot ou à une unité adressable.*

Pour une **mémoire externe**, les données sont souvent transférées en unités plus larges que l'on appelle **bloc**.

♠ Méthode d'accès

1. Accès séquentiel

La mémoire est organisée en unités de données appelées **enregistrements** (*records*) qui sont séparés par des *informations d'adressage*. On utilise un **dispositif de lecture/écriture** qui doit être déplacé séquentiellement de son emplacement courant jusqu'à l'emplacement désiré. Le **temps d'accès** à un emplacement donné **dépend** de la position courante du **dispositif de lecture/écriture**, on dit que le *temps d'accès est variable*.

(*Ex : bandes magnétiques*).

2. Accès direct

Chaque unité de données (*bloc ou enregistrement*) a une adresse unique basée sur son emplacement physique. On utilise un **dispositif de lecture/écriture** afin d'accéder à un emplacement donnée. L'accès se fait en **2 étapes** :

- ❖ Un accès direct à un voisinage de la donnée désirée.

- ❖ Recherche séquentielle, comptage, ou attente pour atteindre la donnée désirée.

*Le temps d'accès est variable.* Ex : Disques durs.

3. Accès aléatoire

Chaque emplacement mémoire adressable possède un mécanisme d'adressage câblé qui est unique, pour accéder à une donnée il suffit de connaître son adresse. *Le temps d'accès à une donnée est constant, indépendant des accès précédents.*

Ex : Mémoire centrale et certains mémoires caches.

4. Accès associatif

Il s'agit d'un type particulier de mémoires à accès aléatoire. Elles sont caractérisées par le fait qu'un mot mémoire est accédé/lu sur base de son contenu et non de son adresse. Comme pour l'accès aléatoire, chaque emplacement adressable a son propre mécanisme d'adressage. *Le temps d'accès à une donnée est constant, indépendant des accès précédents.*

Ex : Mémoires caches.

## ♠ Performance

Elle est caractérisée par 3 paramètres :

### 1. Le temps d'accès

Pour des mémoires à accès aléatoire, il s'agit du **temps pour lire ou écrire une donnée**. Plus précisément, c'est le **temps qui s'écoule** entre le moment où une **adresse est présentée au module mémoire** et le moment où la **donnée correspondante est soit stockée dans la mémoire (écriture)** soit **mise à la disposition du demandeur (lecture)**.

Pour des mémoires à accès non-aléatoire, c'est le temps qu'il faut pour positionner le **mécanisme lecture/écriture** sur l'emplacement que l'on veut accéder.

### 2. Le temps de cycle

Concept principalement appliqué aux **mémoires à accès aléatoire**.

Le **temps de cycle** est la somme du **temps d'accès** et le **temps additionnel** requis pour que la mémoire soit prête pour un autre accès. Ce **temps additionnel** peut provenir de la **stabilisation des lignes de signaux** ou de la **régénération des données lorsque la lecture est destructive**.

Notons que le temps de cycle mémoire est influencé par le bus système et pas par le processeur.

### 3. La vitesse (ou taux) de transfert

C'est la vitesse avec laquelle les données peuvent être transférées *de/vers* la mémoire. Pour une **mémoire à accès aléatoire**, la vitesse est égale à  $\frac{1}{\text{temps de cycle}}$ .

Pour une mémoire à accès non-aléatoire, on a la relation :  $T_N = T_A + \frac{N}{R}$  où

- $T_N$  est le temps moyen pour lire ou écrire N bits.

- $T_A$  est le temps d'accès moyen.

- N est le nombre de bits

- R est la vitesse de transfert en bits par seconde.

## ♠ Le type physique

- Semi-conducteur. Ex : RAM.

- Surface magnétique. Ex : Disques, bandes magnétiques.

- Optique. Ex : CD.

- Etc.

## ♠ Volatile – Non-Volatile

### 1. Mémoires volatiles.

Ce sont des mémoires qui perdent les informations en absence d'électricité. Ex : Mémoires à semi-conducteur.

## 2. Mémoires non-volatiles.

L'information stockée y reste sans détérioration jusqu'à ce qu'elle soit délibérément modifiée, l'électricité n'est donc pas nécessaire pour maintenir celle-ci. Ex : Mémoires à surface magnétique, ROM.

### ♠ Organisation

Cela concerne la manière dont les bits sont physiquement arrangés pour former des mots mémoires, c'est un problème essentiel et non évident dans la construction des mémoires à accès aléatoire.

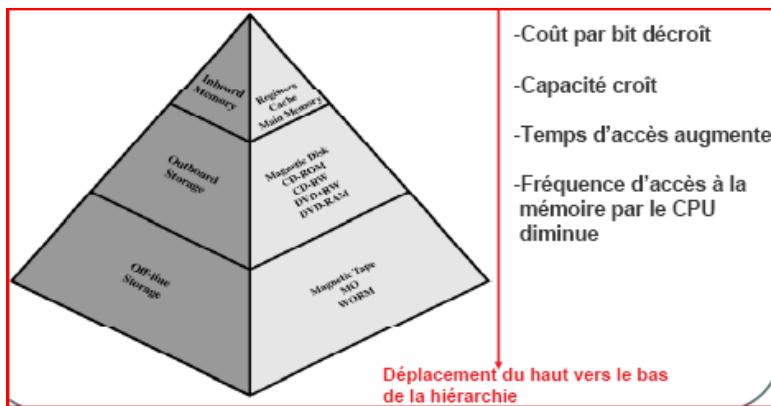

### • Hiérarchie des mémoires.

3 paramètres entre en compte, **la capacité, la rapidité et le coût**. Souvent, un compromis doit être trouvé en exploitant diverses technologies. Le compromis se fonde sur les relations suivantes.

- Plus la mémoire est rapide (*temps d'accès petit*) plus le coup par bit est élevé.

- Plus la capacité de la mémoire est grande, moins le coût par bit est élevé, plus le temps d'accès est long (*mémoire moins rapide*).

La solution à ce dilemme est d'utiliser une **hiérarchie des mémoires**.

### Une hiérarchie typique :

### Impact :

Le succès de cette hiérarchie repose sur l'observation que plus une mémoire se situe loin (plus bas dans la hiérarchie des mémoires) du processeur, moins le processeur y accède souvent. **Avec une hiérarchie des mémoires il est possible de réduire le temps d'accès moyen.**

## Illustration :

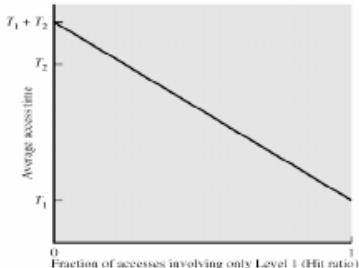

Supposons que le CPU a accès à deux niveaux de mémoire que nous désignons par

- L1

- Ayant 1000 mots et un temps d'accès de  $0.01 \mu\text{s}$

- L2

- Ayant 100000 mots avec un temps d'accès de  $0.1 \mu\text{s}$

### Supposons

- Que le CPU souhaite accéder à un mot de notre mémoire à deux niveaux

- Si le mot mémorié à accéder se trouve en L1, le CPU accède directement à ce mot.

- Si le mot à accéder est dans L2,

- Le mot mémorié est d'abord transféré de L2 vers L1

- Puis le CPU accède au mot à partir de L1

Note: nous ignorons ici le temps qu'il faut au CPU pour déterminer dans quelle mémoire se trouve le mot

Nous voulons avoir une idée de l'évolution du temps d'accès moyen à cette mémoire à deux niveaux

- Évolution du temps d'accès moyen en fonction du nombre d'accès qui sont satisfaits par la mémoire L1

$H$  = la fraction des accès, de tous les accès, qui sont satisfaits par le mémoire de niveau 1 (L1)

$$T_1 = \text{temps d'accès à la mémoire L1} = 0.01 \mu\text{s}$$

$$T_2 = \text{temps d'accès à la mémoire L2} = 0.1 \mu\text{s}$$

Avec  $H = 95\%$ , on a que le temps moyen pour accéder à un mot mémorié pour notre exemple est:  $0.95(0.01 \mu\text{s}) + (0.05)(0.01 \mu\text{s} + 0.1 \mu\text{s}) = 0.015 \mu\text{s}$ , plus proche de  $T_1$ .

## Localité des références :

Nous avons vu que plus on descend dans la hiérarchie des mémoires, moins le processeur accède souvent à l'unité mémoire, cette observation est basée sur le **principe de localité des références**. *Lors de l'exécution d'un programme, les références mémories faites par le CPU tendent à se regrouper pour les raisons suivantes :*

- Les boucles dans les programmes, sous-programmes, etc.

- L'utilisation des tableaux dans des programmes.

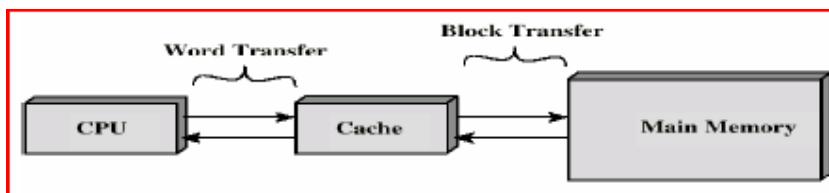

- La mémoire cache.

Il s'agit d'une mémoire à faible capacité mais très rapide, interposée souvent entre le **CPU** et la mémoire principale, elle contient une copie des portions de la mémoire centrale. Son utilisation est motivée par le principe de la **localité des références**.

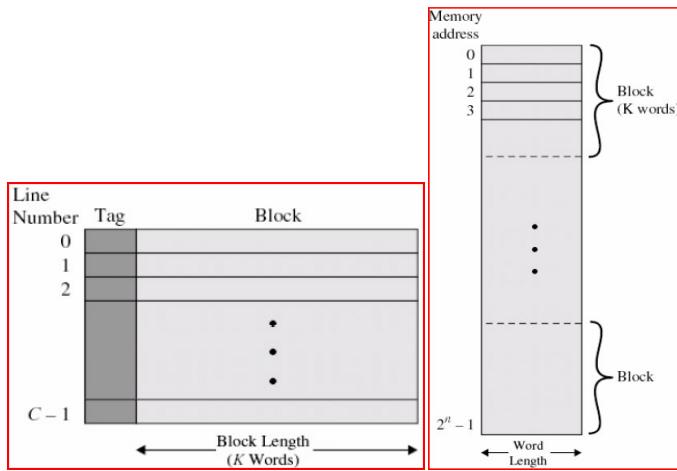

Ex : Voici un cache et la mémoire principale.

Sur cet exemple, chaque mot mémoire a une adresse unique de  $n$  bits. Pour faciliter les transferts vers le cache, la mémoire principale est organisée en blocs de **K mots**, il y a au total **M blocs**. Le cache a quant à lui **C lignes** de **K mots** chacune. « **Tag** » indique le bloc courant stocké dans une ligne (ce « **Tag** » est nécessaire car **C** est très petit par rapport à **M**).

$$C \ll M = \frac{2^n}{K}$$

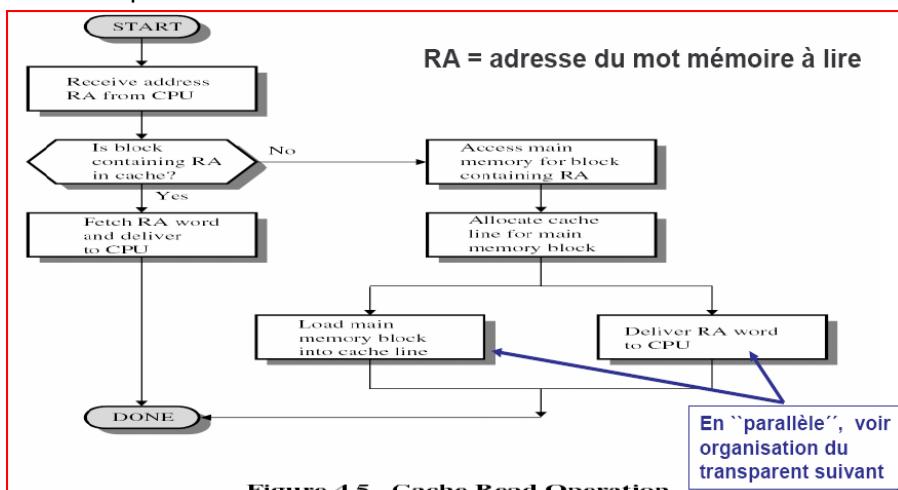

Principe : Lorsque le **CPU** veut lire un mot mémoire, un test est effectué pour déterminer si le mot est dans le cache,

- Si le mot est dans le cache, celui-ci est délivré au **CPU**. → Pas d'accès à la mémoire principale.

- Si le mot n'est pas dans le cache, un bloc de la mémoire principale, contenant le mot désiré, est transféré dans le cache et le mot désiré est fourni au **CPU**.

Grâce au principe de la localité des références, il y a des fortes chances que le prochain mot mémoire que le **CPU** voudra lire sera dans la mémoire cache.

Figure 4.5 Cache Read Operation

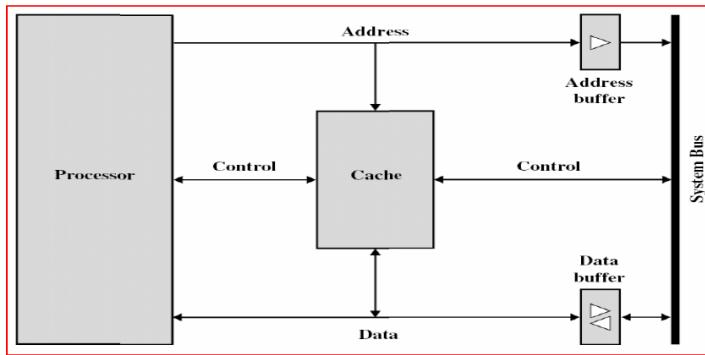

Une organisation typique de la mémoire cache :

Quelques éléments dans la conception du cache.

Taille du cache.

La taille du cache doit être **suffisamment petite** pour que le coût total (*cache+mémoire principale*) par bit soit comparable au coût de la mémoire principale seule et **suffisamment grande** pour que le temps d'accès de l'ensemble soit proche du temps d'accès du cache.

Plus le cache est grand plus il faut de portes logiques pour son adressage.

*Les caches de grande taille tendent à être plus lents que les caches de petite taille.*

Fonctions de correspondance.

*Voir transparents.*

Algorithmes de remplacement.

*Voir transparents.*

Techniques d'écriture : *Voir transparents.*

## 11. Les mémoires internes.

- Mémoires principales à semi-conducteurs.

Les 2 formes de base pour les mémoires à semi-conducteur à accès aléatoire sont la **RAM dynamique (DRAM)** et la **RAM statique (SRAM)**. La **SRAM** est plus rapide, plus coûteuse et moins dense que la **DRAM** et elle est utilisée pour la mémoire cache alors que **DRAM** est utilisée pour la mémoire principale.

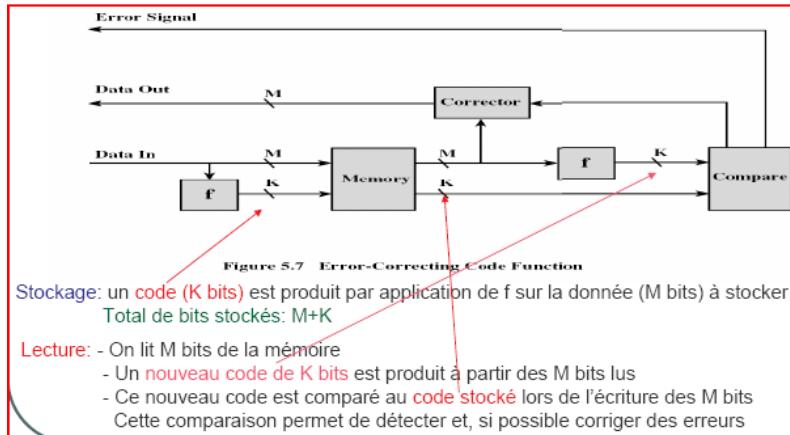

Des techniques de correction d'erreurs sont souvent utilisées dans des systèmes de mémorisation pour améliorer la fiabilité de ces systèmes. Ces techniques sont basées sur l'utilisation de la *redondance*, à chaque séquence de bits de données, on associe un **code correcteur d'erreur** qui consiste en des bits additionnels qui sont fonction des bits de données et lorsqu'un bit de données devient erroné, cela est détecté à l'aide du code et bien souvent corrigé.

Les premiers ordinateurs utilisaient des mémoires principales à tores magnétiques. Avec la microélectronique, l'utilisation des puces à semi-conducteurs est devenue quasi-universelle pour les mémoires principales, on parle alors de **mémoires à semi-conducteurs**.

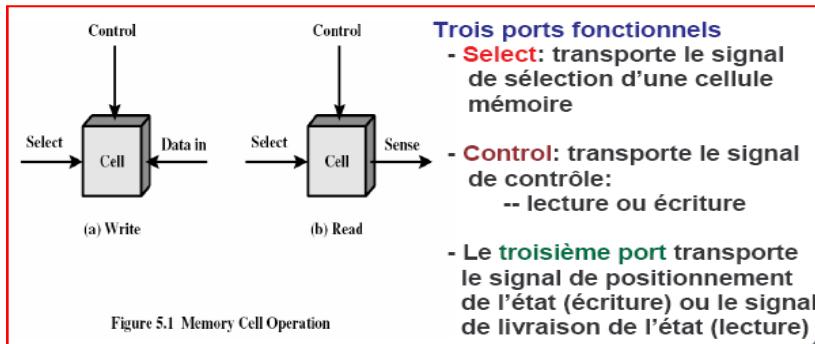

L'élément de base d'une mémoire à semi-conducteurs est la **cellule mémoire**.

- Propriété des cellules mémoires :

2 états stables, qui peuvent être utilisés pour représenter les binaires 1 et 0. On peut y écrire (au moins une fois), pour positionner l'état et on peut les lire pour obtenir l'état.

- Types de mémoire à semi-conducteurs. (toutes des mémoires à accès aléatoire)

| Memory Type                         | Category           | Erasure                   | Write Mechanism | Volatility  |

|-------------------------------------|--------------------|---------------------------|-----------------|-------------|

| Random-access memory (RAM)          | Read-write memory  | Electrically, byte-level  | Electrically    | Volatile    |

| Read-only memory (ROM)              | Read-only memory   | Not possible              | Masks           |             |

| Programmable ROM (PROM)             |                    |                           |                 |             |

| Erasable PROM (EPROM)               | Read-mostly memory | UV light, chip-level      | Electrically    | Nonvolatile |

| Electrically Erasable PROM (EEPROM) |                    | Electrically, byte-level  |                 |             |

| Flash memory                        |                    | Electrically, block-level |                 |             |

- La RAM

Il s'agit de la mémoire à accès aléatoire à semi-conducteur la plus courante, le terme **RAM** est souvent utilisé pour faire référence à la mémoire principale. Ce terme est un peu trompeur car toutes les mémoires à semi-conducteurs listées au transparent précédent sont à accès aléatoire.

- Caractéristiques principales :

Écriture et lecture assez simple et rapide et réalisés au moyen de signaux électriques. La **RAM** est une mémoire volatile et peut donc être utilisée que pour un stockage temporaire d'informations.

Les 2 formes traditionnelles de **RAM** utilisées dans des ordinateurs sont la **DRAM** et la **SRAM**.

### 1. La **DRAM**.

Elle est constituée de cellules de mémoire qui stockent des données sous forme de charge électrique dans des condensateurs (*accumulateurs d'énergie*). La présence ou l'absence de charge est interprétée comme un 1 ou un 0. Les condensateurs ont cependant une tendance naturelle à se décharger, en conséquence la DRAM nécessite un rafraîchissement périodique pour maintenir les données stockées.

- Structure typique d'une cellule DRAM :

- Caractéristiques :

- Plus facile à construire

- Plus dense

- Moins coûteuse

- Plus lente

- Souvent utilisée pour les mémoires principales.

- Une cellule **DRAM** est essentiellement analogique,

Un condensateur peut stocker une valeur d'une charge électrique contenue dans une plage de valeurs, une valeur seuil permettra de déterminer la valeur binaire stockée.

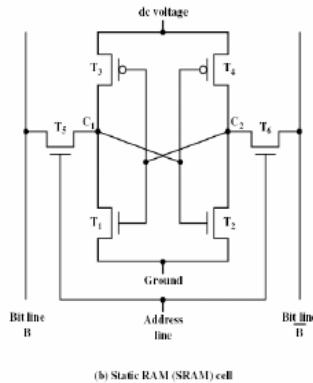

## 2. La SRAM.

- Une mémoire RAM statique (SRAM) est un **composant numérique** utilisant les mêmes éléments logiques que l'on trouve dans le processeur

- Les valeurs binaires sont stockées au moyen des **configurations des bascules**

- Pas de décharge comme dans le cas des DRAM

- Pas besoin de rafraîchissement

- Toute donnée stockée y reste tant qu'il y a du courant

- **Plus complexe**

- **Plus coûteuse**

- Plus rapide

- Souvent utilisée pour des mémoires caches

- Comparaison entre la DRAM et la SRAM.

Elles sont toutes les deux **volatiles**.

Une cellule de mémoire dynamique est plus simple et plus petite qu'une cellule de mémoire statique → la **DRAM** est plus dense.

La **DRAM** est moins coûteuse que la **SRAM** mais elle nécessite un ensemble de circuits de rafraîchissement et est du coup plus lente. Les cellules de la **SRAM** sont faites à l'aide de bascules. La **DRAM** est utilisée pour les mémoires principales et la **SRAM** pour la mémoire cache.

- Les types de ROM

- La ROM

C'est une puce mémoire dans laquelle les données sont enregistrées lors de la fabrication, on peut lire à partir d'une **ROM** mais on ne peut pas y écrire. C'est une **mémoire non-volatile**. Elle est utile pour stocker des programmes critiques, tels que le **BIOS** (*Basic Input/Output System*) qui détermine ce que l'ordinateur peut faire sans accéder aux programmes stockés sur le disque.

- La PROM

C'est une puce mémoire dans laquelle on ne peut écrire qu'une seule fois, donc lorsqu'un programme y est stocké, il y reste (virtuellement) pour toujours. La **PROM** est une mémoire non-volatile, et elle est construite comme une mémoire vide qui est programmable électriquement par le constructeur ou le client, pas nécessairement au moment de la fabrication de la puce, ce qui la rend différente de la **ROM**.

- La mémoire à lecture majoritaire

Il s'agit d'une variante de la **ROM**, elle est utile pour les applications où les opérations de lecture sont plus fréquentes et où une mémoire non volatile est nécessaire. Il en existe 3 formes courantes :

- **EPROM** : *Erasable Programmable Read-Only Memory*

C'est un type spécial de **PROM** qui peut être reprogrammée, pour ce faire il faut tout d'abord l'effacer entièrement en exposant la puce à des rayons **UV**. La lecture et l'écriture se font à l'aide de signaux électriques. L'unique différence avec la **PROM** c'est que l'**EPROM** est **modifiable**.

- **EEPROM** : *Electrically Erasable Programmable Read-Only Memory*

C'est une **PROM** spéciale qui peut être effacée électriquement. On peut y écrire à tout moment sans avoir à effacer toutes les cellules au préalable, les données étant écrites ou effacées un octet à la fois et une écriture prenant plus de temps qu'une lecture. Elle coûte plus chère qu'une mémoire **EPROM** mais elle est moins dense, quelques bits par puce.

- **Flash Memory** : *Mémoire à lecture majoritaire avec effacement très rapide.*

Le nom de flash memory vient du fait qu'une telle mémoire peut être reprogrammée très vite. C'est une mémoire intermédiaire, en termes de coût et fonctionnalité, entre la **EPROM** et la **EEPROM**. Elle est effaçable électriquement comme la **EEPROM** mais plus rapidement, en quelques secondes. Contrairement à une **EEPROM**, la mémoire flash permet d'écrire ou d'effacer uniquement des blocs à la fois, ce qui implique une écriture plus rapide que l'**EEPROM**.

- **Détection et correction d'erreurs.**

- **Erreurs permanentes**

Défectuosités physique affectant une ou plusieurs cellules mémoires, celles-ci une fois affectées ne peuvent plus stocker l'information de manière fiable. Une telle cellule est soit bloquée sur la valeur 1 ou 0, soit elle change arbitrairement entre 1 et 0. De telles erreurs peuvent être causées par des défauts de fabrication ou un mauvais environnement.

- **Erreurs intermittentes**

Ce sont des événements aléatoires, non destructives causant le changement du contenu de une ou plusieurs cellules mémoires, sans endommager la mémoire. Les cellules mémoires affectées ne sont pas détruites, seul leur contenu est changé. Elles peuvent être causées par une coupure de courant ou un petit dérangement temporaire.

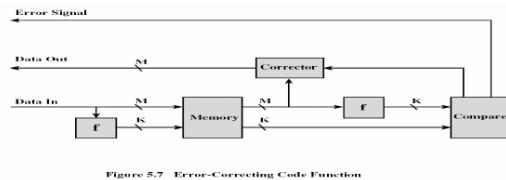

- La logique illustrée

Résultat de la comparaison :

- Aucune erreur n'est détectée → les bits lus sont envoyés au module demandeur.

- Une erreur corrigible est détectée → Les  $M$  bits et le code stockés sont passés au correcteur, qui corrige l'erreur et envoie la donnée corrigée au module demandeur.

- Une erreur non corrigible est détectée → Un rapport est retourné au module demandeur.

Les codes opérants de cette façon sont appelés **codes correcteurs d'erreurs**, ces codes sont caractérisés par le nombre de bits erronés, dans un mot, qu'ils permettent de détecter et de corriger.

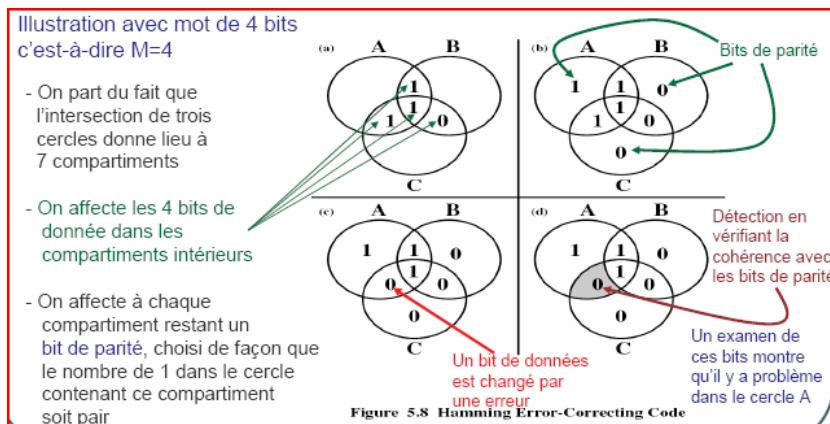

- Le code de Hamming

C'est l'un des codes les plus simples. Illustration :

Pour mettre en évidence les concepts sous-jacents au code de **Hamming**, développons un code de **Hamming** capable de détecter et corriger un seul bit erroné sur des mots de 8 bits (c à d M=8).

### Etape 1: détermination de la longueur du code

- Le comparateur reçoit deux entrées de K bits

- La comparaison bit par bit se fait à l'aide du OU-EXCLUSIF des deux entrées

- Le résultat de cette comparaison est appelé **mot syndrome**

- **Exemple** de comparaison bit par bit à l'aide du **OU-EXCLUSIF** (noté  $\oplus$ )

$$\begin{array}{r} 0 \ 1 \ 1 \ 1 \\ \oplus \ 0 \ 0 \ 0 \ 1 \\ \hline \text{Mot syndrome} = \ 0 \ 1 \ 1 \ 0 \end{array}$$

Le bit en position  $i$  du mot syndrome est

1: si les deux bits comparés en position  $i$  sont différents

0: si les deux bits comparés en position  $i$  sont égaux

Cet exemple montre que le **mot syndrome** aura le même nombre de bits que chacune des chaînes de bits comparées

Le **mot syndrome** a **K bits** de long, sa valeur décimale peut donc être une des valeurs  $\in \{0,1,2,\dots,2^k-1\}$ . On va donc utiliser ces valeurs de la façon suivante :

- La valeur **0** indique qu'aucune erreur n'a été détectée

- Les valeurs **1,2,...,2<sup>k</sup>-1** servent à indiquer en cas d'erreur, que bit est erroné et puisque le bit erroné peut être un des  $M+K$  bits, nous devons avoir  $2^k-1 \geq M+K$  (\*\*).

L'inégalité (\*\*) nous donne le nombre de bits nécessaires pour corriger un seul bit erroné dans un mot de données contenant M bits. Ex : pour M=8, nous avons :

- Pour  $K=3$ ,  $2^3-1 = 7 \geq 8+3$ , la relation (\*\*) n'est pas satisfaite. On ne peut donc pas prendre  $K=3$ .

- Pour  $K=4$ ,  $2^4-1 = 15 \geq 8+4$ , la relation (\*\*) est satisfaite, donc avec 8 bits de données (M) nous avons besoin de 4 bits de code (K).

| Data Bits | Single-Error Correction |            | Single-Error Correction/<br>Double-Error Detection |            |

|-----------|-------------------------|------------|----------------------------------------------------|------------|

|           | Check Bits              | % Increase | Check Bits                                         | % Increase |

| 8         | 4                       | 50         | 5                                                  | 62.5       |

| 16        | 5                       | 31.25      | 6                                                  | 37.5       |

| 32        | 6                       | 18.75      | 7                                                  | 21.875     |

| 64        | 7                       | 10.94      | 8                                                  | 12.5       |

| 128       | 8                       | 6.25       | 9                                                  | 7.03       |

| 256       | 9                       | 3.52       | 10                                                 | 3.91       |

- Caractéristiques du mot syndrome.

Pour notre exemple, générions le mot syndrome de 4 bits pour 8 bits de données avec les contraintes suivantes :

- Si le mot syndrome ne contient que des 0, alors aucune erreur n'est détectée.

- Si le mot syndrome contient un et un seul bit mis à 1, alors il y a une erreur dans un des 4 bits de contrôle (code). (*Aucune correction n'est requise*)

- Si le mot syndrome contient plus d'un bit mis à 1, alors la valeur numérique du mot syndrome indique la position du bit de donnée erronée